양자 컴퓨팅은 이제 가속 컴퓨팅과 양자 프로세서의 긴밀한 통합을 통해 진정한 발전을 이루는 새로운 국면에 접어들고 있습니다. 양자 처리 장치(QPU)를 제어하고 측정하는 하드웨어는 실시간 보정부터 양자 오류 정정(QEC) 디코딩까지 높은 수준의 계산 성능을 요구합니다. 실용적인 양자 응용을 실현하려면, 이러한 QEC와 보정 과정을 고성능 가속 컴퓨팅과 유기적으로 결합해 대규모로 수행할 수 있어야 합니다.

NVIDIA NVQLink는 가속 컴퓨팅을 양자 시스템에 직접 통합하여, 오늘날의 GPU 슈퍼칩이 QPU의 실시간 워크로드를 직접 처리할 수 있습니다.

NVQLink는 기존 슈퍼컴퓨팅 호스트와 양자 시스템 제어기(QSC)를 유기적으로 연결하는 개방형 플랫폼 아키텍처입니다. 초전도, 이온 포획, 광자, 스핀 기반 등 현재 업계 전반에서 사용되는 다양한 제어 시스템과 호환되며, QPU와 제어기 개발자가 기술적 창의성과 확장성을 충분히 발휘할 수 있는 유연성을 제공합니다. 핵심 목표는 슈퍼컴퓨팅 노드를 QPU 환경의 핵심 구성 요소로 통합함으로써, 양자 하드웨어의 계산 역량을 비약적으로 끌어올리는 것입니다.

NVQLink 시스템 및 소프트웨어 아키텍처

NVQLink 아키텍처는 Logical QPU라는 새로운 머신 모델을 소개합니다(그림 1 참조). 이는 물리적 큐비트와 이를 제어하고 판독하는 전자 장치, QEC 디코딩과 연속 보정 등 실시간으로 처리해야 하는 컴퓨팅 작업까지 모두 포함하는 완전한 시스템입니다. 이 구성 요소들은 실시간 호스트와 양자 시스템 제어기를 저지연, 고확장성의 실시간 인터커넥트로 연결해, 오류 허용 양자 컴퓨터의 런타임 워크로드를 실시간으로 처리할 수 있는 네트워크 환경을 구성합니다.

이 하이브리드 시스템은 양자 코히런트 제어 기술과 최신 슈퍼컴퓨팅 기술을 하나로 통합합니다. 한쪽에는 NVIDIA CUDA-Q 플랫폼을 통해 C++ 또는 Python으로 프로그래밍 가능한 가속 컴퓨팅 노드인 실시간 호스트가 있고, 다른 한쪽에는 서드파티 양자 시스템 제어기(QSC)가 위치합니다. 이 제어기는 FPGA나 RFSoC 기반의 펄스 처리 유닛(PPU)을 활용해 큐비트를 정밀하게 제어합니다. 이 두 구성 요소는 저지연·고대역폭의 실시간 인터커넥트로 연결되며, 이를 통해 양자 하드웨어의 동작 시간 범위 내에서 필요한 계산 작업을 실시간으로 수행할 수 있습니다.

실시간 인터커넥트는 컨트롤러에 탑재된 오픈소스 FPGA 코어(네트워크 인터페이스 역할을 하는 NI 위젯)를 통해 RDMA over Ethernet 방식으로 구현할 수 있으며, CUDA-Q 런타임과 연동하여 <4마이크로초 지연 시간 내에 컴파일된 데이터를 교환하는 실시간 콜백(fn 위젯)을 지원합니다.

애플리케이션 개발자에게 Logical QPU는 CUDA와 CUDA-Q가 지원하는 슈퍼컴퓨팅 환경에서 새롭게 등장한 이기종 디바이스 유형입니다. 이러한 구조는 QPU 개발자에게 논리적 QPU에 필요한 CPU, GPU, PPU 전부를 동일한 이기종 프로그래밍 모델을 통해 타깃팅할 수 있다는 장점이 있습니다.

개발자는 표준 C++ 또는 Python 문법을 사용해 양자 커널과 실시간 호스트에 대한 콜백을 함께 표현하는 단일 프로그램을 작성할 수 있습니다. CUDA-Q에 새롭게 도입된 cudaq::device_call 기능을 통해 양자 커널 내에서 GPU나 CPU 함수를 직접 호출하고, 그 결과를 마이크로초 단위로 받습니다. 이 설계는 익숙한 CUDA의 이기종 프로그래밍 모델을 양자 영역으로 확장하여, 기존의 복잡한 다중 언어 및 REST 기반 제어 스택에서 벗어나 네이티브 고성능 통합이 지원됩니다.

다음 코드는 cudaq::device_call이 포함된 단일 양자 커널로 구현된 실시간 QEC 메모리 실험의 예제입니다.

__qpu__ void adaptive_qec_kernel(cudaq::qvector<>& data_qubits,

cudaq::qvector<>& ancilla_qubits,

int cycles) {

for(int = 0; i < cycles; ++i){

// Stabilizer circuits here

...

// Execute syndrome extraction measurements

auto syndrome = mz(ancilla_qubits);

// Real-time streaming to dedicated GPU

cudaq::device_call(/*gpu_id=*/1,

surface_code_enqueue,

syndrome);

// Repeat

}

// Real-time decode on dedicated GPU

auto correction = cudaq::device_call(/*gpu_id=*/1,

surface_code_decode);

// Apply corrections physically if desired (typically tracked in software)

if (correction.x_errors.any())

apply_pauli_x_corrections(data_qubits, correction.x_errors);

if (correction.z_errors.any())

apply_pauli_z_corrections(data_qubits, correction.z_errors);

}

기저 런타임은 정적 다형성과 트레잇 기반 구성(trait-based composition)을 활용해, 성능에 민감한 경로에서의 오버헤드를 제거합니다. GPU, CPU, FPGA 등 각 디바이스는 호출 가능한 함수와 데이터 버퍼를 런타임에 등록하며, 이를 통해 데이터 전달이 매끄럽게 이뤄지고 지연 시간은 최소화됩니다.

이러한 기술적 혁신을 통해 NVQLink는 QPU를 느린 API를 통해 접근하는 주변 장치에서, 슈퍼컴퓨터 내에서 동등한 일급 컴퓨팅 자원으로 탈바꿈시킵니다. 즉, 양자 컴퓨팅과 기존 컴퓨팅이 하나의 시스템 내에서 지연 시간이 제한된 환경 속에 공존할 수 있으며, 진정한 하이브리드 가속 양자 슈퍼컴퓨터를 실현합니다.

표준 기술 기반의 초고속 네트워킹

실시간 인터커넥트는 NVQLink의 핵심 성능을 뒷받침하는 중요한 기반입니다. RDMA over Converged Ethernet(RoCE) 방식을 통해 구현되며, 범용 이더넷 인프라를 그대로 활용하면서도 최신 수준의 성능을 확보할 수 있습니다.

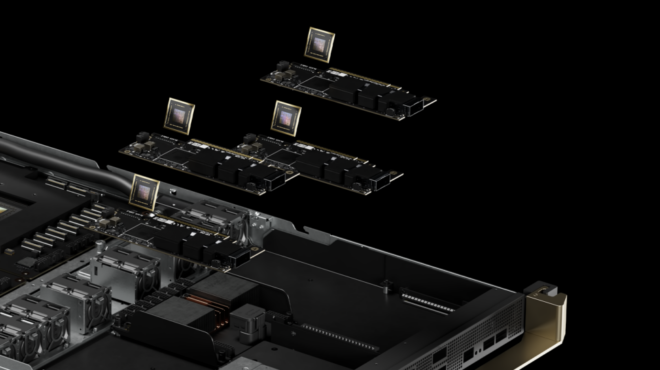

이 접근 방식은 상용 부품으로 구성된 NVQLink 시스템에서 입증되었습니다. 여기에는 RFSoC FPGA, Arm 기반 호스트, NVIDIA RTX PRO 6000 Blackwell Max-Q Workstation Edition GPU, 그리고 NVIDIA ConnectX-7 네트워크 인터페이스 카드가 사용되었습니다(그림 2 참조). FPGA와 호스트 간 데이터 전송에는 NVIDIA Holoscan Sensor Bridge(HSB)와 Holoscan SDK(HSDK)가 사용되어, FPGA의 데이터를 호스트 소프트웨어로, 또는 그 반대로 안정적으로 전달합니다.

FPGA는 정밀 시간 프로토콜(PTP) 카운터로 타임스탬프가 지정된 RoCE 패킷을 생성하며, 이 패킷은 DOCA GPUNetIO를 사용하는 지속 실행 CUDA 커널을 통해 GPU에서 루프백됩니다. 이 시스템의 종단 간 지연 시간은 평균 3.84마이크로초, 표준 편차 0.035마이크로초, 최대 3.96마이크로초(1,000회 샘플 기준)로 측정되었습니다. 이 수준의 낮은 지연 시간과 지터는 현재뿐만 아니라 미래의 오류 허용 QEC 디코딩 및 기타 실시간 제어 작업에 충분히 적합한 성능입니다.

이 간단한 네트워킹 구성—FPGA 측에는 오픈소스 경량 RoCE 코어를, 호스트 측에는 표준 NVIDIA 네트워킹 하드웨어를 사용하는 방식—은 슈퍼컴퓨팅 센터에 널리 배포된 동일한 기술을 활용해 QPU 및 QSC 개발자들이 NVQLink를 즉시 실용적으로 적용할 수 있습니다. FPGA IP는 자유롭게 제공되며, 독점 펌웨어를 공개할 필요가 없어 개발자는 자신의 지적 재산을 보호하면서 NVIDIA가 지원하는 검증된 고성능 전송 계층에 접근할 수 있습니다.

무엇보다 이 방식은 확장성을 갖추고 있습니다. 최신 슈퍼컴퓨팅 센터의 이더넷 장비는 이미 400 Gbit/s 링크와 256포트 스위치 라디스를 지원합니다. 대규모 AI 및 슈퍼컴퓨팅 구축 사례가 RDMA 기술의 발전을 계속해서 이끄는 가운데, 이러한 혁신은 NVQLink를 통해 통합되는 양자 시스템에도 직접적인 혜택을 제공합니다.

실시간 디코딩: Quantinuum Helios와 NVIDIA NVQLink

NVQLink는 이미 양자 컴퓨팅 에코시스템의 선도 기업들에 의해 채택되고 있습니다. QPU 개발사인 Quantinuum은 향후 자사 프로세서에 NVQLink를 적용할 계획이라고 발표했으며, 최근 공개된 Helios QPU는 실시간 호스트로 NVIDIA GH200 Grace Hopper를 탑재한 상태로 배포되고 있습니다. GH200 서버는 CUDA-Q QEC 라이브러리의 신드롬 디코더를 활용해 실시간 양자 오류 정정을 수행합니다.

CUDA-Q의 nv-qldpc-decoder는 Helios의 올투올(all-to-all) 연결 구조를 활용할 수 있어, 양자 저밀도 패리티 검사(qLDPC) 코드 연구를 지원합니다. 이는 오류 허용 양자 컴퓨팅의 오버헤드를 줄일 수 있는 가능성을 보여줍니다. Helios는 어떤 qLDPC 코드도 실행할 수 있으며, NVIDIA 디코더는 Helios에서 모든 qLDPC 코드를 실시간으로 디코딩할 수 있습니다.

NVIDIA 팀은 Quantinuum과 협력하여 이 기능을 입증했습니다. 우리는 Bring’s 코드라는 고율 qLDPC 코드를 디코딩했으며, 이는 8개의 논리 큐비트를 30개의 물리 큐비트에 인코딩하는 방식입니다. 이 실험에는 BP+OSD(Belief Propagation + Ordered Statistics Decoding) 디코딩 알고리즘이 사용되었으며, 중앙값 67마이크로초의 디코딩 시간을 기록해 실시간 오류 정정과 피드포워드 보정을 안정적으로 처리할 수 있었습니다.

이 코드를 이용해 8 논리 큐비트 기반의 논리 메모리를 구성하고, Helios에서 3라운드의 양자 오류 정정을 수행한 결과, 8개의 논리 큐비트는 0.925±0.38%의 오류율을 기록했으며, 이는 디코딩 이전의 4.95±0.67%에 비해 5.4배 개선된 성능입니다.

이번 성과는 NVQLink가 차세대 양자 컴퓨팅의 핵심 인프라로 자리잡을 수 있음을 시사합니다.

NVQLink 시작하기

NVIDIA NVQLink는 보다 확장 가능한 양자 시스템을 설계, 구축, 배포하는 과정에서 빠른 실험과 긴밀한 피드백 루프를 지원합니다. 오픈하고 표준 기반의 인터페이스를 찾는 QPU 개발자, 차세대 디코딩 및 보정 알고리즘을 연구하는 연구자, 차세대 양자 애플리케이션을 개발하는 운영자 모두에게 NVQLink는 로드맵을 가속화할 수 있는 강력한 기반을 제공합니다.

NVQLink는 양자 컴퓨팅 업계 전반의 파트너들과의 협력을 통해 구축된 개방형 플랫폼입니다.

지금 바로 시작해 보세요

- 고성능 컴퓨팅과 양자 프로세서의 긴밀한 결합을 위한 플랫폼 아키텍처에 대한 기술 문서를 확인해 보세요.

- CUDA-Q 오픈소스 SDK와 CUDA-Q QEC 라이브러리를 통해 직접 실험해 보세요.

- 더 많은 정보를 확인하고 NVIDIA 팀과 직접 연결해 보세요.