P3710 Networking

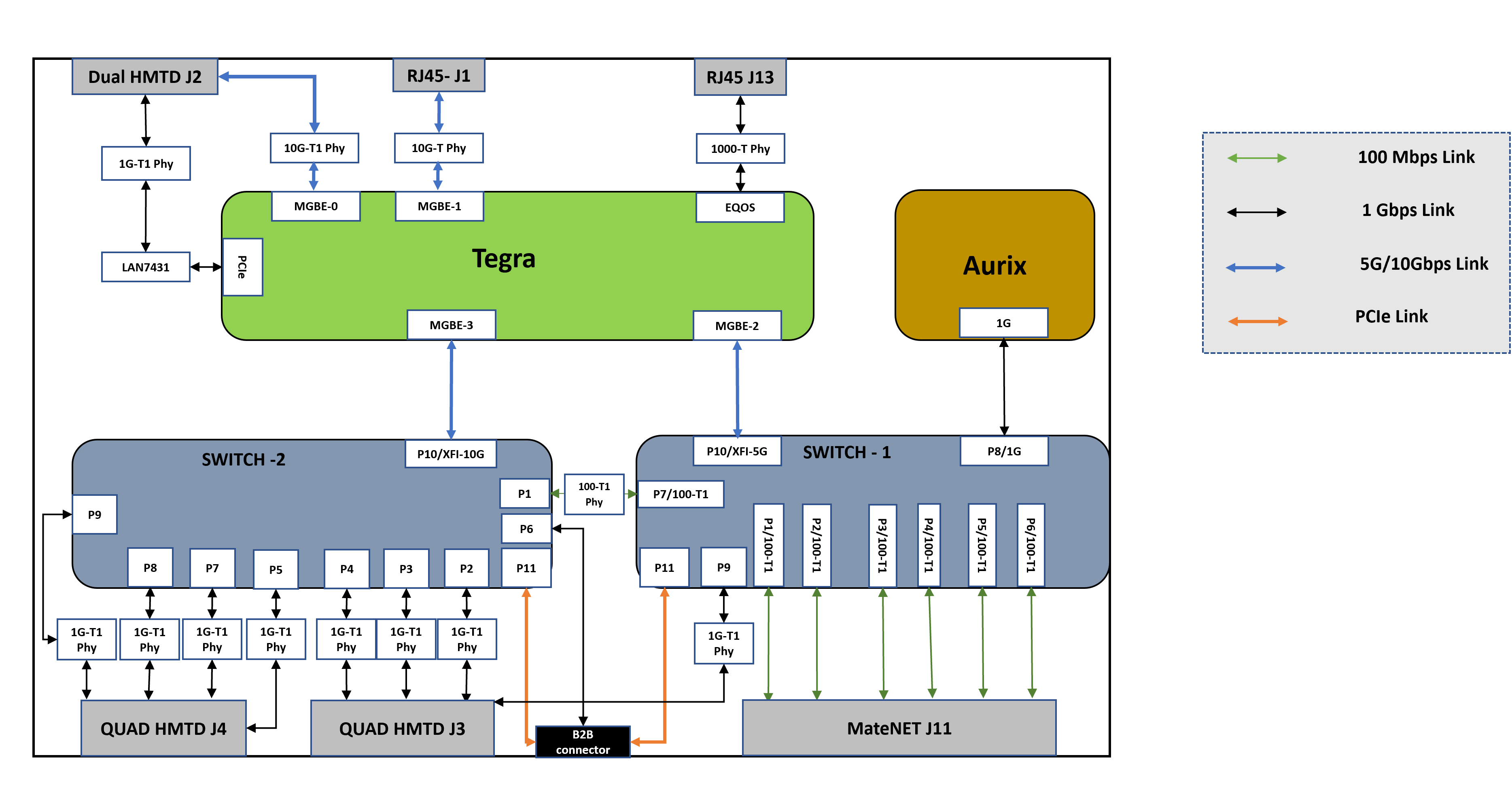

The following diagram shows the P3710 network topology:

Board External Connectors

(Common for both P3663 and P3710)

Matenet

Matenet connector has connection for Port 1 to Port 6 of Oak switch.

QUAD HMTD

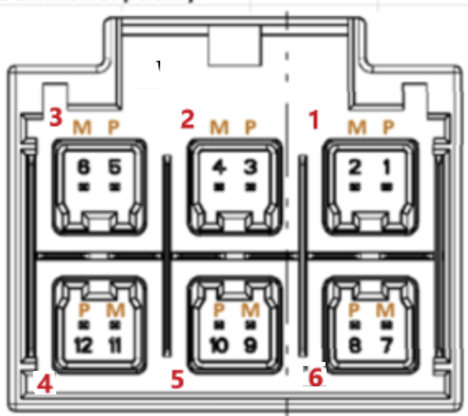

The following is the channel map of HMTD:

External Connector Port: Mapping to Switch/Controller

QUAD HMTD Connector J3

| Port | Connected to |

|---|---|

| 1 | Switch-1 (88Q5072) Port 9 |

| 2 | Switch-2 (88Q6113) Port 2 |

| 3 | Switch-2 (88Q6113) Port 3 |

| 4 | Switch-2 (88Q6113) Port 4 |

QUAD HMTD Connector J4

| Port | Connected to |

|---|---|

| 1 | Switch-2 (88Q6113) Port 5 |

| 2 | Switch-2 (88Q6113) Port 7 |

| 3 | Switch-2 (88Q6113) Port 8 |

| 4 | Switch-2 (88Q6113) Port 9 |

Dual HMTD Connector J2

| Port | Connected to |

|---|---|

| 1 | Tegra MGBE0 Ethernet Controller |

| 2 | LAN7431 (PCIe Ethernet Controller) |

| Port | Pin Number | Connected to |

|---|---|---|

| 1 | Pin 1&2 | Switch (88Q5072) Port 1 |

| 2 | Pin 3&4 | Switch (88Q5072) Port 2 |

| 3 | Pin 5&6 | Switch (88Q5072) Port 3 |

| 4 | Pin 11&12 | Switch (88Q5072) Port 4 |

| 5 | Pin 9&10 | Switch (88Q5072) Port 5 |

| 6 | Pin 7&8 | Switch (88Q5072) Port 6 |

Network Configuration

DRIVE OS 6.0 supports two network configurations named Base and Safety. Base configuration is applicable to standard PCD configuration i.e., AV+L Standard and AV+Q Standard, while Safety is applicable for AV+Q prod, Prod_debug, and prod_debug_extra. These switch configurations are controlled by the AURIX MCU firmware via AURIX command line.

The configuration selection is enabled via AURIX MCU AUTOSAR firmware commands. Commands details:

getnetworkconfig : Get the current network config info

setnetworkconfig <config value>: Sets network config for next MCU boot

Where the <config value> parameter is as below:

| Configuration | Value | Orin PCT (applicable) | Max MTU supported (MGBE2-OAK) | PTP support in OAK Switch | Switch Over the air update support |

|---|---|---|---|---|---|

| NW_CFG_BASE | 0 | AV+L & AV+Q standard | Up to 16Kbytes | Yes (Refer PTP section) | Yes |

| NW_CFG_BASE_SAFETY | 1 | AV+Q Safety | 1500 bytes | Bypass (Switch CPU disable) | No |

The major difference use cases between NW_CFG_BASE and NW_CFG_BASE_SAFETY are:

- Switch CPU & Firmware disabled : In safety platform configurations, Marvell switch CPU (QM) and firmware (ASIL NA) are disabled to achieve DRIVE OS time sync safety goals.

- Max MTU size: In safety platform configurations, The max MTU size in MGBE2 and OAK switch is reduced to ~1500. To minimize the PTP bypass latency time in safety.

- OTA support: In safety, Marvell switch CPU is disabled. Therefore, there is no OTA support for Marvell switches.

Networking Port Configuration

| Node | Controller/Switch Port | Mode & Speed | T1 Role | PHY present | L2 switch forwarding restriction |

|---|---|---|---|---|---|

| Tegra | EQOS | 1G-BASE-T | NA | Yes | NA |

| MGBE-0 | 10G-BASE-T1 | Primary | Yes | NA | |

| MGBE-1 | 10G-BASE-T | NA | Yes | NA | |

| MGBE-2 | 5G (XFI) | NA | No | NA | |

| MGBE-3 | 10G (XFI) | NA | No | NA | |

| Switch-1 (88Q5072) | P0 (Internal CPU port) | 1G | NA | No | No Restriction |

| P1 | 100M-BASE-T1 | Primary | Yes (internal) | No Restriction except forwarding to Switch-1 P8 | |

| P2 | 100M-BASE-T1 | Primary | Yes (internal) | No Restriction except forwarding to Switch-1 P8 | |

| P3 | 100M-BASE-T1 | Primary | Yes (internal) | No Restriction except forwarding to Switch-1 P8 | |

| P4 | 100M-BASE-T1 | Primary | Yes (internal) | No Restriction except forwarding to Switch-1 P8 | |

| P5 | 100M-BASE-T1 | Primary | Yes (internal) | No Restriction except forwarding to Switch-1 P8 | |

| P6 | 100M-BASE-T1 | Primary | Yes (internal) | No Restriction except forwarding to Switch-1 P8 | |

| P7 | 100M-BASE-T1 | Primary | Yes (internal) | No Restriction except forwarding to Switch-1 P8 | |

| P8 | 1G (RGMII) | NA | No | Only to P10 | |

| P9 | 1G-BASE-T1 | Primary | Yes | No Restriction except forwarding to Switch-1 P8 | |

| P10 | 5G (XFI) | NA | No | No Restriction | |

| P11 | PCIe Gen3 X1 | NA | No | No Restriction except forwarding to Switch-1 P8 | |

| Switch-2 (88Q6113) | P0 (Internal CPU port) | 1G | NA | No | No Restriction |

| P1 | 1G-BASE-T1 | Secondary | Yes | No Restriction | |

| P2 | 1G-BASE-T1 | Primary | Yes | No Restriction | |

| P3 | 1G-BASE-T1 | Primary | Yes | No Restriction | |

| P4 | 1G-BASE-T1 | Primary | Yes | No Restriction | |

| P5 | 1G-BASE-T1 | Primary | Yes | No Restriction | |

| P6 | SGMII | NA | No | No Restriction | |

| P7 | 1G-BASE-T1 | Primary | Yes | No Restriction | |

| P8 | 1G-BASE-T1 | Primary | Yes | No Restriction | |

| P9 | 1G-BASE-T1 | Primary | Yes | No Restriction | |

| P10 | 10G (XFI) | NA | No | No Restriction | |

| P11 | PCIe Gen3 X2 | NA | No | No Restriction | |

| Tegra PCIe Ethernet | LAN 7431 controller | 1G-BASE-T1 | Master | Yes | NA |