Architecture

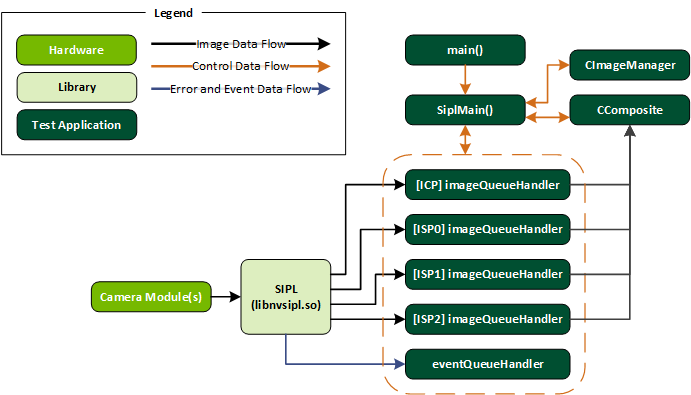

The following diagram shows the architecture of the nvsipl_sample application.

The test application executes the SiplMain() function in which it uses the INvSIPLCamera interface for communicating with the NvSIPL library and uses the CImageManager class for buffer allocation and deallocation.

The platform configuration used by the application is fixed; all output types are enabled for one image processing pipeline. This pipeline captures and processes images from a single camera module.

The calibration data for the image processing pipeline is provided in the form of an NVIDIA Image Tuning Object (NITO) file in the target file system. NITO files are binary files that contain ISP settings, tuning settings, and characterization parameters for a specific camera module.

The main thread, executing the SiplMain() function, initializes the image processing pipeline using the NvSIPL APIs and then spawns a series of different threads. One thread is created for receiving the errors and events from the NvSIPL library and printing them to the command line. Other individual threads are created for receiving the output buffers for each of the output types of the pipeline. All these threads receive their associated items (either events or image buffers) by retrieving these items from queues provided by the NvSIPL library.

The received buffers contain an image and its associated metadata. Each image output thread reads the frame sequence number from the image metadata structure and prints it to the command line, then releases the buffer for subsequent capture and processing operations.