Debugging CSI Capture Errors

Note:

All commands in this section must run as root user (with sudo).

The terms used throughout this section are as follows:

- CCPLEX: NVIDIA Carmel CPU complex running the capture stack and applications.

- CRC: Cyclic Redundancy Check, a 16-bit checksum present in MIPI CSI packet footer.

- ECC: Error Correction Code, a 6-bit code present in MIPI CSI packet header that can be used by the receiver to correct single bit errors and detect double bit errors.

- NVCSI: An SoC MIPI CSI interface conformant to CSI2 v2.0 specification.

- RCE: Realtime Camera Engine is an ARM Cortex R5 core running an RTOS that handles programming of NVCSI/VI engines and notify messages from VI.

- VI: An SoC Video Input module that takes frame data from NVCSI interface and writes it to memory.

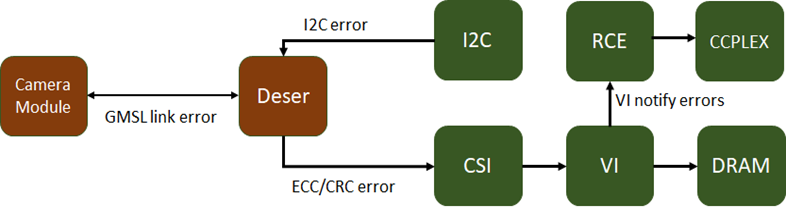

The layers where errors can occur during a camera capture are as follows:

Deserializer Errors

Two signals that can be generated by Deserializer are as follows:

- ERRB

- LOCK

If these signals are toggled, SIPL sends error notification to the client, and the client collects the detailed error information from the hardware.