Primary/Secondary Capture#

The unique use case where you can run nvsipl_camera on one NVIDIA DRIVE AGX Orin/Thor™ (primary Orin/Thor) and have the same image frames captured on the second NVIDIA DRIVE AGX Thor (secondary Orin/Thor) if your platform supports this.

When running this use case, nvsipl_camera running on primary Thor needs to specify the camRecCfg option to have the image frames sent to the secondary Orin. Instead of using the MAX96712/MAX96724/MAX96792A deserializer replication feature on the CSI output ports, this camRecCfg option will be used to configure the deserializer to forward the image frames from cameras to the specific CSI output ports on MAX96712/MAX96724/MAX96792A directly.

There are two supported configurations for camRecCfg.

–camRecCfg 1#

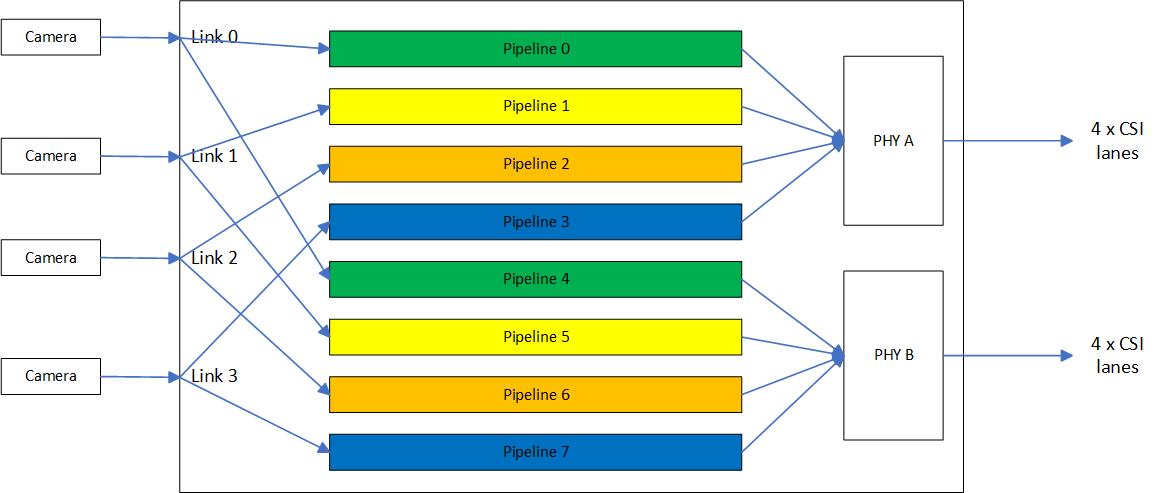

MAX96712

Primary Thor is connected to PHY A and secondary Thor is connected to PHY B. Frames from the camera on the link 0 are forwarded to Pipeline 0 and 4, and frames from the camera on the link 1 are forwarded to Pipeline 1 and 5, and so on. Data from pipeline 0 to 3 are output at PHY A in 4 x CSI lanes, while data from Pipeline 4 to 7 are output at PHY B in 4 x CSI lanes, followed by enabling CSI outputs at both PHY A and B on the deserializer.

MAX96724/MAX96792A

Primary Tegra is connected to PHY A and secondary Tegra is connected to PHY B and copies data from PHY A to PHY B.

–camRecCfg 2#

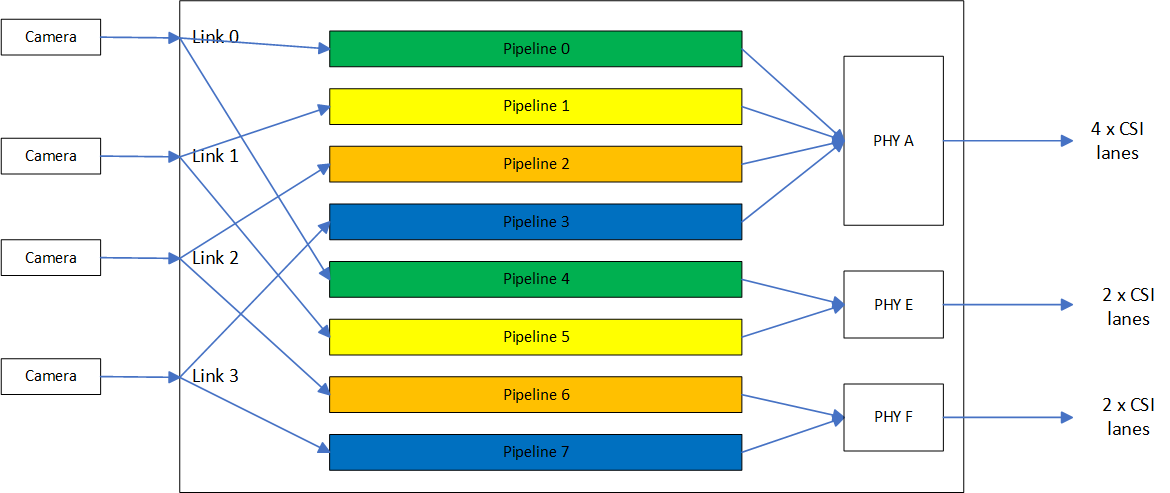

MAX96712

Primary Thor is connected to PHY A and secondary Thor is connected to PHY E and/or PHY F. Frames from the camera on the link 0 are forwarded to Pipeline 0 and 4, and frames from the camera on the link 1 are forwarded to Pipeline 1 and 5, and so on. Data from Pipeline 0 to 3 are output at PHY A in 4 x CSI lanes, while data from Pipeline 4 to 5 are output at PHY E in 2 x CSI lanes and data from Pipeline 6 to 7 are output at PHY F in 2 x CSI lanes following by enabling CSI outputs at both PHY A and B on the deserializer.

MAX96724/MAX96792A

This option is not supported with MAX96724/MAX96792A deserializer.