# NVIDIA TensorRT 8.6.10 Developer Guide

for DRIVE OS | NVIDIA Docs

# **Table of Contents**

| Revision History                               | ix |

|------------------------------------------------|----|

| Chapter 1. Introduction                        | 1  |

| 1.1. Structure of This Guide                   | 1  |

| 1.2. Samples                                   | 1  |

| 1.3. Complementary GPU Features                | 1  |

| 1.4. Complementary Software                    | 2  |

| 1.5. ONNX                                      | 2  |

| 1.6. Code Analysis Tools                       | 3  |

| 1.7. API Versioning                            | 3  |

| 1.8. Deprecation Policy                        | 3  |

| 1.9. Hardware Support Lifetime                 | 4  |

| 1.10. Support                                  | 4  |

| 1.11. Reporting Bugs                           | 4  |

| Chapter 2. TensorRT's Capabilities             | 5  |

| 2.1. C++ and Python APIs                       |    |

| 2.2. The Programming Model                     | 5  |

| 2.2.1. The Build Phase                         | 5  |

| 2.2.2. The Runtime Phase                       | 6  |

| 2.3. Plugins                                   | 7  |

| 2.4. Types and Precision                       | 7  |

| 2.5. Quantization                              | 8  |

| 2.6. Tensors and Data Formats                  | 8  |

| 2.7. Dynamic Shapes                            | 8  |

| 2.8. DLA                                       | 9  |

| 2.9. Updating Weights                          | 9  |

| 2.10. trtexec Tool                             | 9  |

| 2.11. Polygraphy                               | 10 |

| Chapter 3. The C++ API                         | 11 |

| 3.1. The Build Phase                           | 11 |

| 3.1.1. Creating a Network Definition           | 11 |

| 3.1.2. Importing a Model Using the ONNX Parser | 12 |

| 3.1.3. Building an Engine                      | 12 |

| 3.2. Deserializing a Plan                      | 13 |

| 3.3. Performing Inference                      | 13 |

| Chapter 4. The Python API                      | 15 |

| 4.1. The Build Phase              |                              | 15 |

|-----------------------------------|------------------------------|----|

| 4.1.1. Creating a Network De      | efinition in Python          | 15 |

| 4.1.2. Importing a Model Usi      | ng the ONNX Parser           | 16 |

| 4.1.3. Building an Engine         |                              | 16 |

| 4.2. Deserializing a Plan         |                              | 16 |

| 4.3. Performing Inference         |                              | 17 |

| Chapter 5. How TensorRT Wor       | -ks                          | 18 |

| 5.1. Object Lifetimes             |                              | 18 |

| 5.2. Error Handling and Loggin    | ng                           | 18 |

| 5.3. Memory                       |                              | 19 |

| 5.3.1. The Build Phase            |                              | 19 |

| 5.3.2. The Runtime Phase          |                              | 19 |

| 5.3.3. CUDA Lazy Loading          |                              | 21 |

| 5.3.4. L2 Persistent Cache M      | lanagement                   | 21 |

| 5.4. Threading                    |                              | 21 |

| 5.5. Determinism                  |                              | 22 |

| 5.5.1. IFillLayer Determinism.    |                              | 22 |

| 5.6. Runtime Options              |                              | 22 |

| 5.7. Compatibility                |                              | 23 |

| Chapter 6. Advanced Topics        |                              | 24 |

| 6.1. Version Compatibility        |                              | 24 |

| 6.1.1. Manually Loading the       | Runtime                      | 25 |

| 6.1.2. Loading from Storage.      |                              | 25 |

| 6.1.3. Using Version Compati      | ibility with the ONNX Parser | 25 |

| 6.2. Hardware Compatibility       |                              | 26 |

| 6.3. Compatibility Checks         |                              | 26 |

| 6.4. Refitting an Engine          |                              | 27 |

| 6.5. Algorithm Selection and Re   | eproducible Builds           | 29 |

| 6.6. Creating a Network Definit   | tion from Scratch            | 30 |

| 6.6.1. C++                        |                              | 30 |

| 6.6.2. Python                     |                              | 31 |

| 6.7. Reduced Precision            |                              | 33 |

| 6.7.1. Network-Level Control      | of Precision                 | 33 |

| 6.7.2. Layer-Level Control of     | Precision                    | 34 |

| 6.7.3. TF32                       |                              | 35 |

| 6.8. I/O Formats                  |                              | 36 |

| 6.9. Explicit Versus Implicit Bat | tch                          | 37 |

| 6.10. Sparsity                    |                              | 38 |

| 6.11. E | mpty Tensors                                                    | 39 |

|---------|-----------------------------------------------------------------|----|

| 6.12. F | Reusing Input Buffers                                           | 40 |

| 6.13. E | Engine Inspector                                                | 40 |

| 6.14. F | Preview Features                                                | 42 |

| Chapter | 7. Working with INT8                                            | 43 |

| 7.1. In | troduction to Quantization                                      | 43 |

| 7.1.1   | . Quantization Workflows                                        | 44 |

| 7.1.2   | 2. Explicit Versus Implicit Quantization                        | 44 |

| 7.1.3   | 3. Per-Tensor and Per-Channel Quantization                      | 45 |

| 7.2. Se | etting Dynamic Range                                            | 46 |

| 7.3. Pc | st-Training Quantization Using Calibration                      | 46 |

| 7.3.1   | I. INT8 Calibration Using C++                                   | 48 |

| 7.3.2   | 2. Calibration Using Python                                     | 49 |

| 7.3.3   | 3. Quantization Noise Reduction                                 | 49 |

| 7.4. Ex | plicit Quantization                                             | 50 |

| 7.4.1   | . Quantized Weights                                             | 50 |

| 7.4.2   | 2. ONNX Support                                                 | 50 |

| 7.4.3   | 3. TensorRT Processing of Q/DQ Networks                         | 51 |

| 7.4.4   | 1. Q/DQ Layer-Placement Recommendations                         | 53 |

| 7.4.5   | 5. Q/DQ Limitations                                             | 58 |

| 7.4.6   | S. Q/DQ Interaction with Plugins                                | 59 |

| 7.4.7   | 7. QAT Networks Using TensorFlow                                | 60 |

| 7.4.8   | 3. QAT Networks Using PyTorch                                   | 60 |

| 7.5. IN | T8 Rounding Modes                                               | 60 |

| Chapter | 8. Working with Dynamic Shapes                                  | 61 |

| 8.1. Sp | pecifying Runtime Dimensions                                    | 62 |

| 8.2. Na | amed Dimensions                                                 | 63 |

| 8.3. Di | mension Constraint using IAssertionLayer                        | 64 |

| 8.4. Op | otimization Profiles                                            | 64 |

| 8.5. Dy | namically Shaped Output                                         | 66 |

| 8.5.1   | . Looking up Binding Indices for Multiple Optimization Profiles | 68 |

| 8.5.2   | 2. Bindings For Multiple Optimization Profiles                  | 68 |

| 8.6. La | yer Extensions For Dynamic Shapes                               | 69 |

| 8.7. Re | estrictions For Dynamic Shapes                                  | 70 |

| 8.8. Ex | ecution Tensors Versus Shape Tensors                            | 70 |

|         | I. Formal Inference Rules                                       |    |

|         | nape Tensor I/O (Advanced)                                      |    |

| 8 10 H  | NT8 Calibration with Dynamic Shapes                             | 73 |

| Chapter 9. Extending TensorRT with Custom Layers                           | 75  |

|----------------------------------------------------------------------------|-----|

| 9.1. Adding Custom Layers Using the C++ API                                | 75  |

| 9.1.1. Example: Adding a Custom Layer with Dynamic Shape Support Using C++ | 77  |

| 9.1.2. Example: Adding a Custom Layer with INT8 I/O Support Using C++      | 79  |

| 9.2. Adding Custom Layers Using the Python API                             | 81  |

| 9.2.1. Example: Adding a Custom Layer to a TensorRT Network Using Python   | 8   |

| 9.3. Using Custom Layers When Importing a Model with a Parser              | 82  |

| 9.4. Plugin API Description                                                | 82  |

| 9.4.1. Migrating Plugins from TensorRT 6.x or 7.x to TensorRT 8.x.x        | 82  |

| 9.4.2. IPluginV2 API Description                                           | 83  |

| 9.4.3. IPluginCreator API Description                                      | 85  |

| 9.5. Best Practices for Custom Layers Plugin                               | 86  |

| 9.5.1. Coding Guidelines for Plugins                                       | 86  |

| 9.5.2. Using Plugins in Implicit/Explicit Batch Networks                   | 87  |

| 9.5.3. Communicating Shape Tensors to Plugins                              | 87  |

| 9.6. Plugin Shared Libraries                                               | 88  |

| 9.6.1. Generating Plugin Shared Libraries                                  | 88  |

| 9.6.2. Using Plugin Shared Libraries                                       | 89  |

| Chapter 10. Working with Loops                                             | 90  |

| 10.1. Defining a Loop                                                      | 90  |

| 10.2. Formal Semantics                                                     | 93  |

| 10.3. Nested Loops                                                         | 93  |

| 10.4. Limitations                                                          | 94  |

| 10.5. Replacing IRNNv2Layer with Loops                                     | 94  |

| Chapter 11. Working with Conditionals                                      | 95  |

| 11.1. Defining a Conditional                                               | 95  |

| 11.2. Conditional Execution                                                | 97  |

| 11.3. Nesting and Loops                                                    | 98  |

| 11.4. Limitations                                                          | 99  |

| 11.5. Conditional Examples                                                 | 99  |

| 11.5.1. Simple If-Conditional                                              | 99  |

| 11.5.2. Exporting from PyTorch                                             | 100 |

| Chapter 12. Working with DLA                                               | 101 |

| 12.1. Building and Launching the Loadable                                  |     |

| 12.1.1. Using trtexec                                                      |     |

| 12.1.2. Using the TensorRT API                                             |     |

| 12.1.2.1. Running on DLA during TensorRT Inference                         | 103 |

| 12.1.2.2 Example: Run Samples with DLA                                     | 104 |

| 12.1.2.3. Example: Enable DLA Mode for a Layer during Network Creation | 104 |

|------------------------------------------------------------------------|-----|

| 12.1.3. Using the cuDLA API                                            | 105 |

| 12.2. DLA Supported Layers and Restrictions                            | 105 |

| 12.2.1. General Restrictions                                           | 105 |

| 12.2.2. Layer Support and Restrictions                                 | 106 |

| 12.2.3. Inference on NVIDIA Orin                                       | 110 |

| 12.3. GPU Fallback Mode                                                | 110 |

| 12.4. I/O Formats on DLA                                               | 110 |

| 12.5. DLA Standalone Mode                                              | 111 |

| 12.5.1. Building A DLA Loadable Using C++                              | 111 |

| 12.5.1.1. Using trtexec To Generate A DLA Loadable                     | 112 |

| 12.6. Customizing DLA Memory Pools                                     | 112 |

| 12.6.1. Determining DLA Memory Pool Usage                              | 113 |

| 12.7. Sparsity on DLA                                                  | 113 |

| 12.7.1. Structured Sparsity                                            | 113 |

| Chapter 13. Performance Best Practices                                 | 114 |

| 13.1. Measuring Performance                                            | 114 |

| 13.1.1. Wall-clock Timing                                              | 115 |

| 13.1.2. CUDA Events                                                    | 115 |

| 13.1.3. Built-In TensorRT Profiling                                    | 116 |

| 13.1.4. CUDA Profiling Tools                                           | 116 |

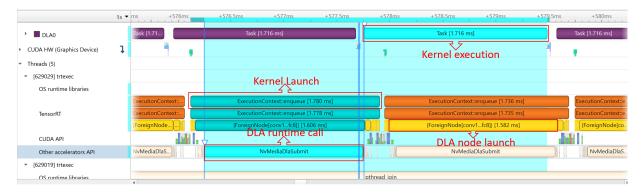

| 13.1.4.1. Profiling for DLA                                            | 121 |

| 13.1.5. Tracking Memory                                                | 122 |

| 13.2. Hardware/Software Environment for Performance Measurements       | 122 |

| 13.2.1. GPU Information Query and GPU Monitoring                       | 123 |

| 13.2.2. GPU Clock Locking and Floating Clock                           | 123 |

| 13.2.3. GPU Power Consumption and Power Throttling                     | 124 |

| 13.2.4. GPU Temperature and Thermal Throttling                         | 124 |

| 13.2.5. H2D/D2H Data Transfers and PCle Bandwidth                      | 125 |

| 13.2.6. TCC Mode and WDDM Mode                                         | 126 |

| 13.2.7. Enqueue-Bound Workloads and CUDA Graphs                        | 126 |

| 13.2.8. BlockingSync and SpinWait Synchronization Modes                | 127 |

| 13.3. Optimizing TensorRT Performance                                  | 128 |

| 13.3.1. Batching                                                       | 128 |

| 13.3.2. Within-Inference Multi-Streaming                               | 129 |

| 13.3.3. Cross-Inference Multi-Streaming                                | 131 |

| 13.3.4. CUDA Graphs                                                    | 131 |

| 13.3.5. Enabling Fusion                                                | 132 |

| 13.3.5.1. Layer Fusion                                              | 132 |

|---------------------------------------------------------------------|-----|

| 13.3.5.2. Types of Fusions                                          | 133 |

| 13.3.5.3. PointWise Fusion                                          | 135 |

| 13.3.5.4. Q/DQ Fusion                                               | 136 |

| 13.3.6. Limiting Compute Resources                                  | 137 |

| 13.3.7. Deterministic Tactic Selection                              | 137 |

| 13.3.8. Transformers Performance                                    | 138 |

| 13.3.9. Overhead of Shape Change and Optimization Profile Switching | 140 |

| 13.4. Optimizing Layer Performance                                  | 140 |

| 13.5. Optimizing for Tensor Cores                                   | 142 |

| 13.6. Optimizing Plugins                                            | 143 |

| 13.7. Optimizing Python Performance                                 | 143 |

| 13.8. Improving Model Accuracy                                      | 144 |

| 13.9. Optimizing Builder Performance                                | 145 |

| 13.9.1. Timing Cache                                                | 145 |

| 13.9.2. Tactic Selection Heuristic                                  | 146 |

| 13.10. Builder Optimization Level                                   | 146 |

| Chapter 14. Troubleshooting                                         | 147 |

| 14.1. FAQs                                                          |     |

| 14.2. Understanding Error Messages                                  | 150 |

| 14.3. Code Analysis Tools                                           | 154 |

| 14.3.1. Compiler Sanitizers                                         | 154 |

| 14.3.1.1. Issues with dlopen and Address Sanitizer                  | 154 |

| 14.3.1.2. Issues with dlopen and Thread Sanitizer                   | 155 |

| 14.3.1.3. Issues with CUDA and Address Sanitizer                    | 155 |

| 14.3.1.4. Issues with Undefined Behavior Sanitizer                  | 155 |

| 14.3.2. Valgrind                                                    | 155 |

| 14.3.3. Compute Sanitizer                                           | 155 |

| 14.4. Understanding Formats Printed in Logs                         | 156 |

| 14.5. Reporting TensorRT Issues                                     | 156 |

| 14.5.1. Channels for TensorRT Issue Reporting                       | 157 |

| 14.5.2. Reporting a Functional Issue                                | 158 |

| 14.5.3. Reporting an Accuracy Issue                                 | 158 |

| 14.5.4. Reporting a Performance Issue                               | 159 |

| Appendix A. Appendix                                                | 160 |

| A.1. Data Format Descriptions                                       |     |

| A.2. Command-Line Programs                                          |     |

| Δ 3. Glossary                                                       | 170 |

# **Revision History**

This is the revision history of the NVIDIA TensorRT 8.6.10 Developer Guide for DRIVE OS.

#### Chapter 2 Updates

| Date             | Summary of Change                                  |

|------------------|----------------------------------------------------|

| January 17, 2023 | Added a footnote to the <u>Types and Precision</u> |

|                  | topic.                                             |

#### Chapter 3 Updates

| Date             | Summary of Change                             |

|------------------|-----------------------------------------------|

| January 17, 2023 | Updated the <u>Performing Inference</u> topic |

|                  | regarding executing a network.                |

#### Chapter 4 Updates

| Date             | Summary of Change                                                                                                                                                                       |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| January 17, 2023 | <ul> <li>Updated the <u>Building an Engine</u> topic regarding insufficient workspace.</li> <li>Updated the <u>Performing Inference</u> topic regarding executing a network.</li> </ul> |

#### Chapter 5 Updates

| Date             | Summary of Change                                    |

|------------------|------------------------------------------------------|

| January 19, 2023 | Added a new topic called <u>Runtime Options</u> .    |

| January 24, 2023 | Rewrote the existing <u>CUDA Lazy Loading</u> topic. |

| March 8, 2023    | Added a new topic called <u>Compatibility</u> .      |

### Chapter 6 Updates

| Date              | Summary of Change                                                                            |

|-------------------|----------------------------------------------------------------------------------------------|

| January 24, 2023  | <ul> <li>Added a new topic called <u>Version</u></li> <li><u>Compatibility</u>.</li> </ul>   |

|                   | <ul> <li>Added a new topic called <u>Manually Loading</u><br/>the <u>Runtime</u>.</li> </ul> |

|                   | Added a new topic called <u>Loading from</u><br><u>Storage</u> .                             |

|                   | <ul> <li>Added a new topic called <u>Hardware</u></li> <li><u>Compatibility</u>.</li> </ul>  |

| February 14, 2023 | Rewrote the existing <u>Compatibility Checks</u> topic.                                      |

| March 8, 2023     | Added a new topic called <u>Using Version</u> <u>Compatibility with the ONNX Parser.</u>     |

### Chapter 7 Updates

| Date             | Summary of Change                                               |

|------------------|-----------------------------------------------------------------|

| January 17, 2023 | Added a new topic called <u>Q/DQ Interaction with Plugins</u> . |

### Chapter 8 Updates

| Date             | Summary of Change                                    |

|------------------|------------------------------------------------------|

| January 24, 2023 | Added a new topic called <u>Dimension Constraint</u> |

|                  | using IAssertionLayer.                               |

### Chapter 9 Updates

| Date             | Summary of Change                                                     |

|------------------|-----------------------------------------------------------------------|

| January 28, 2023 | Added a new section called <u>Plugin Shared</u><br><u>Libraries</u> . |

### Chapter 13 Updates

| Date             | Summary of Change                                                            |

|------------------|------------------------------------------------------------------------------|

| January 29, 2023 | Added a new topic called <u>Within-Inference</u><br><u>Multi-Streaming</u> . |

| Date | Summary of Change                                                                         |

|------|-------------------------------------------------------------------------------------------|

|      | Rewrote the Streaming topic and renamed<br>it to <u>Cross-Inference Multi-Streaming</u> . |

|      | Added a Python example to <u>CUDA Graphs</u> .                                            |

|      | Added a new topic called <u>Builder</u> Optimization Level.                               |

### Appendix Updates

| Date             | Summary of Change                                                                                                       |

|------------------|-------------------------------------------------------------------------------------------------------------------------|

| January 17, 2023 | Added more flags to the build and inference phase sections of the <u>Commonly Used</u> <u>Command-line Flags</u> topic. |

# List of Figures

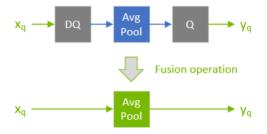

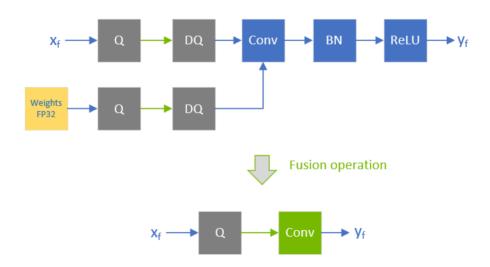

| Figure 1. A quantizable AveragePool layer (in blue) is fused with a DQ layer and a Q layer. All three layers are replaced by a quantized AveragePool layer (in green)                                                                                                         | 51   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

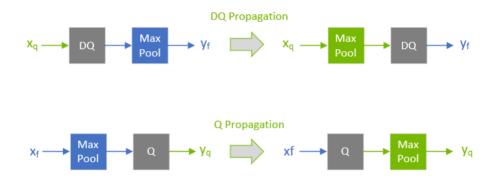

| Figure 2. An illustration depicting a DQ forward-propagation and Q backward-propagation                                                                                                                                                                                       | . 52 |

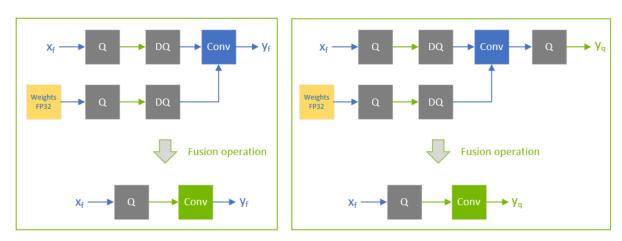

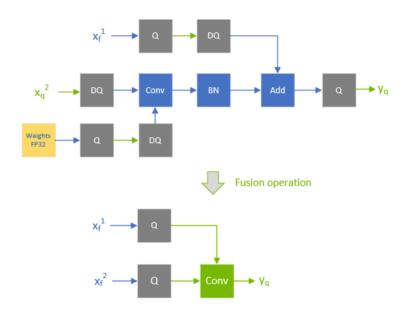

| Figure 3. Two examples of how TensorRT fuses convolutional layers. On the left, only the inputs are quantized. On the right, both inputs and output are quantized                                                                                                             | .54  |

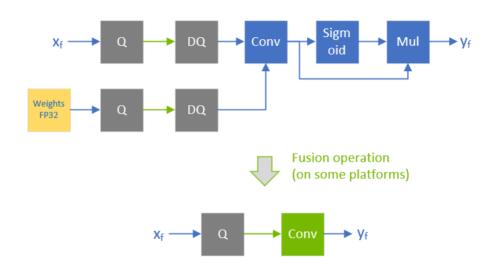

| Figure 4. Example of a linear operation followed by an activation function                                                                                                                                                                                                    | . 54 |

| Figure 5. Batch normalization is fused with convolution and ReLU while keeping the same execution order as defined in the pre-fusion network. There is no need to simulate BN-folding in the training network                                                                 | . 55 |

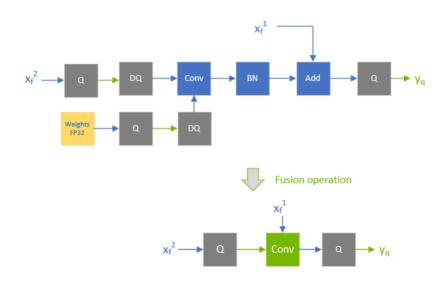

| Figure 6. The precision of xf1 is floating point, so the output of the fused convolution is limited to floating-point, and the trailing Q-layer cannot be fused with the convolution                                                                                          | . 56 |

| Figure 7. When xf1 is quantized to INT8, the output of the fused convolution is also INT8, and the trailing Q-layer is fused with the convolution                                                                                                                             | . 56 |

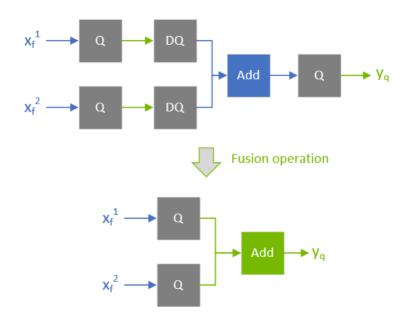

| Figure 8. An example of quantizing a quantizable operation. An element-wise addition is fused with the input DQs and the output Q                                                                                                                                             | .57  |

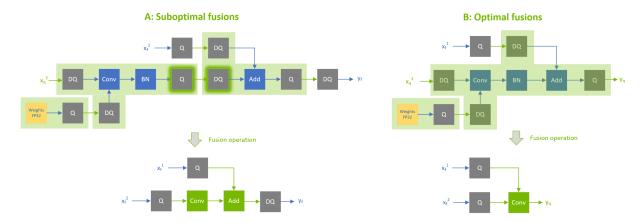

| Figure 9. An example of suboptimal quantization fusions: contrast the suboptimal fusion in A and the optimal fusion in B. The extra pair of Q/DQ operations (highlighted with a glowing-green border) forces the separation of the convolution from the element-wise addition | 58   |

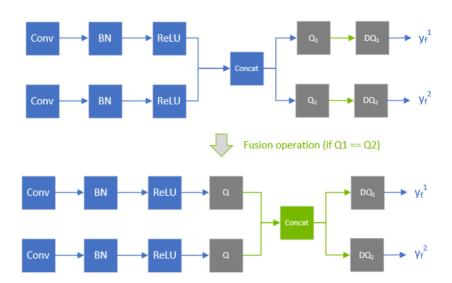

| Figure 10. An example showing scales of Q1 and Q2 are compared for equality, and if equal, they are allowed to propagate backward. If the engine is refitted with new values for Q1 and Q2 such that Q1 != Q2, then an exception aborts the refitting process                 | 59   |

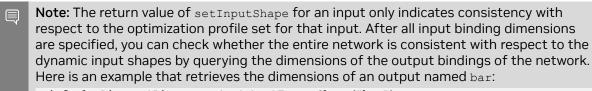

| Figure 11. Optimization Profile                                                                                                                                                                                                                                               | 69   |

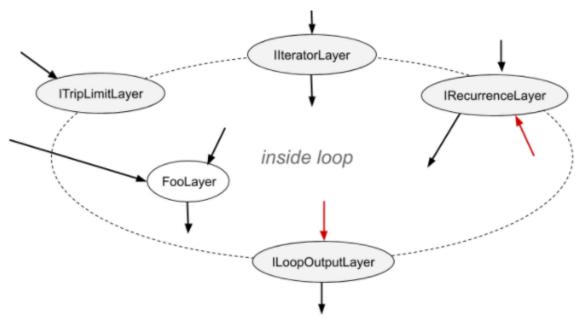

| Figure 12. A TensorRT loop is set by loop boundary layers. Dataflow can leave the loop only by ILoopOutputLayer. The only back edges allowed are the second input to IRecurrenceLayer                                                                                         | . 91 |

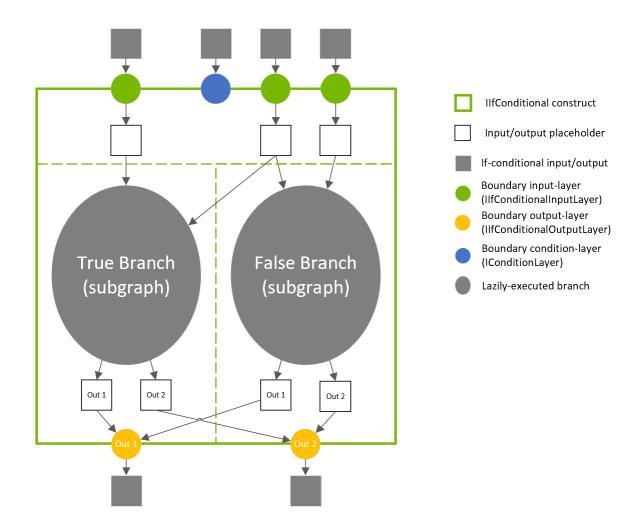

| Figure 13. An If-Conditional Construct Abstract Model                                                                                                                                                                                                                         | 97   |

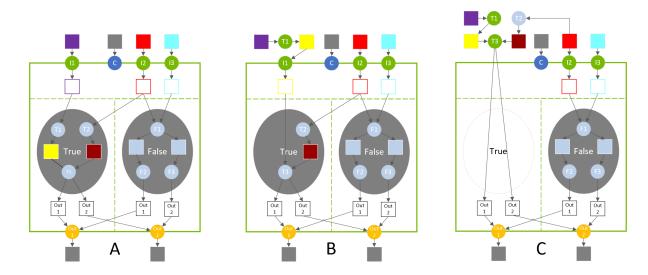

| _          | Controlling Conditional-Execution using IIfConditionalInputLayer              | 98  |

|------------|-------------------------------------------------------------------------------|-----|

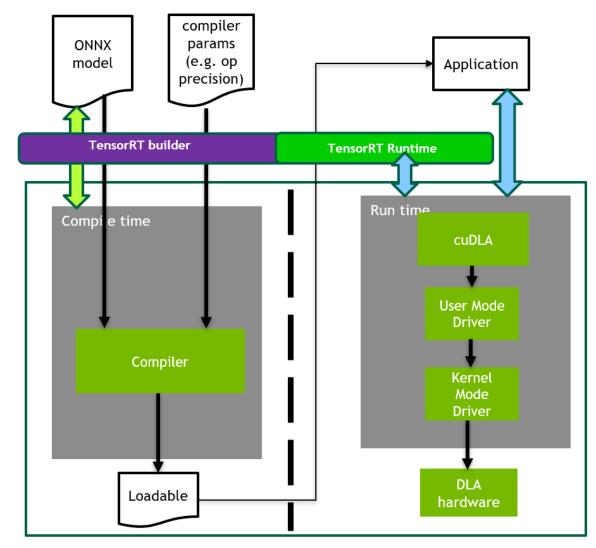

| Figure 15. | Workflow for the Building and Runtime Phases of DLA                           | 102 |

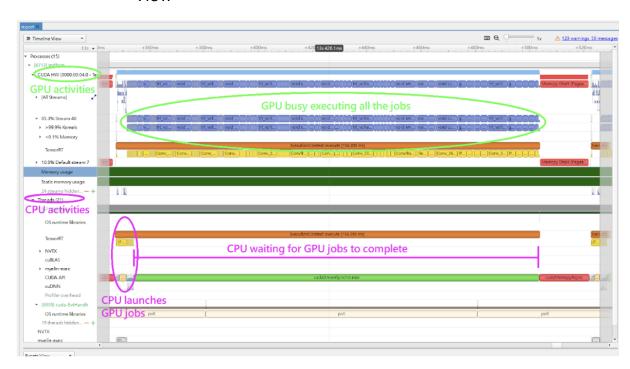

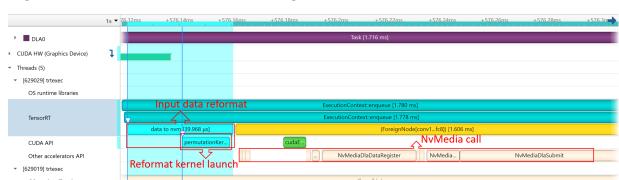

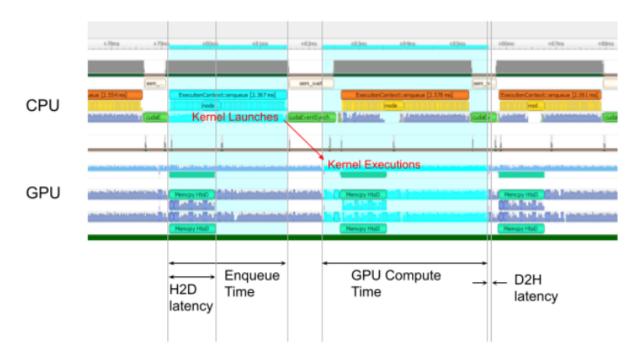

| Figure 16. | Normal Inference Workloads in Nsight Systems Timeline View                    | 118 |

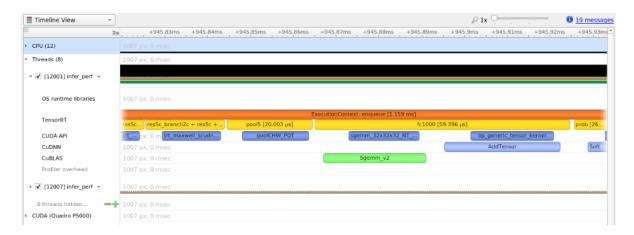

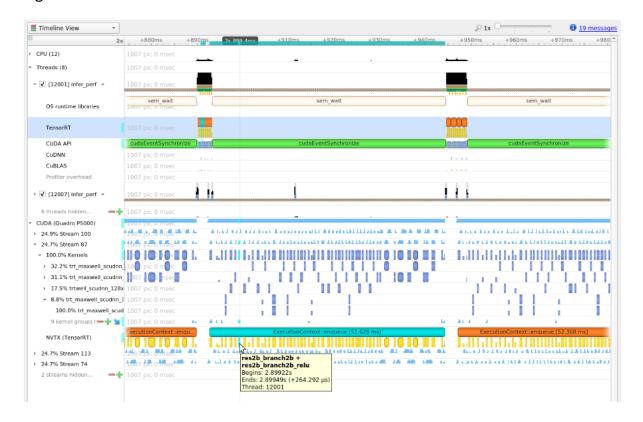

| Figure 17. | The Layer Execution and the Kernel Being Launched on the CPU Side             | 119 |

| Figure 18. | The Kernels Run on the GPU                                                    | 119 |

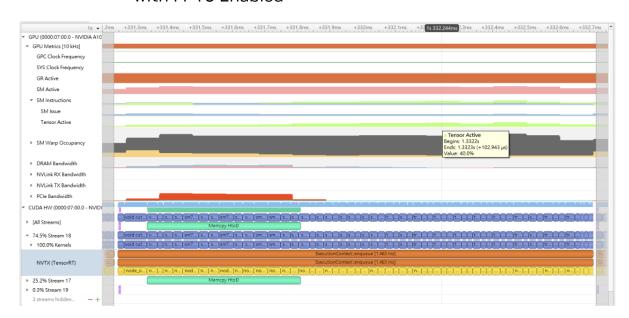

| Figure 19. | Sample DLA Profiling Report                                                   | 121 |

| Figure 20. | Sample DLA Profiling report                                                   | 122 |

| _          | Tensor Core Activities on an A100 GPU Running ResNet-50 with FP16             | 143 |

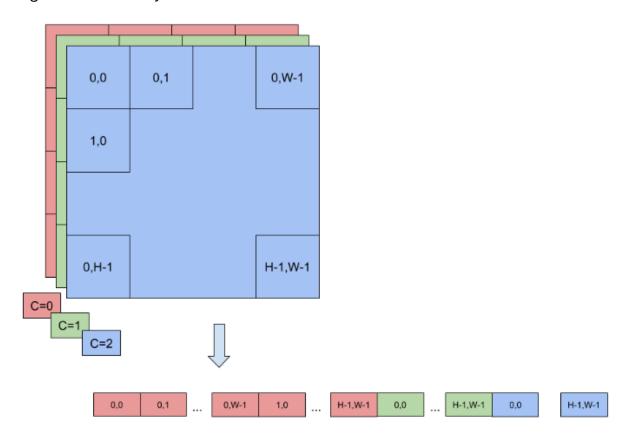

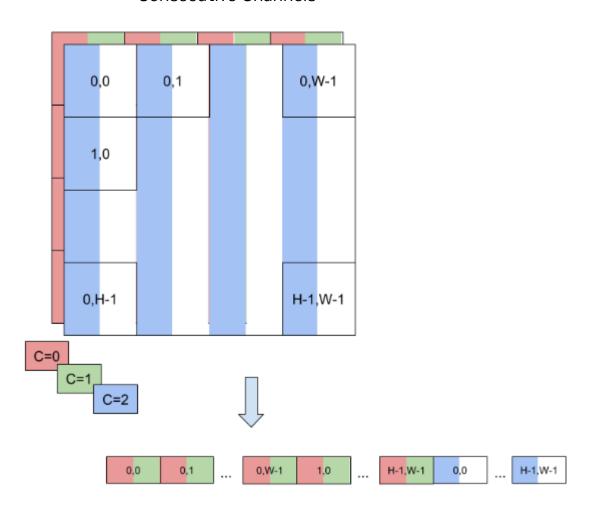

| Figure 22. | Layout Format for CHW                                                         | 161 |

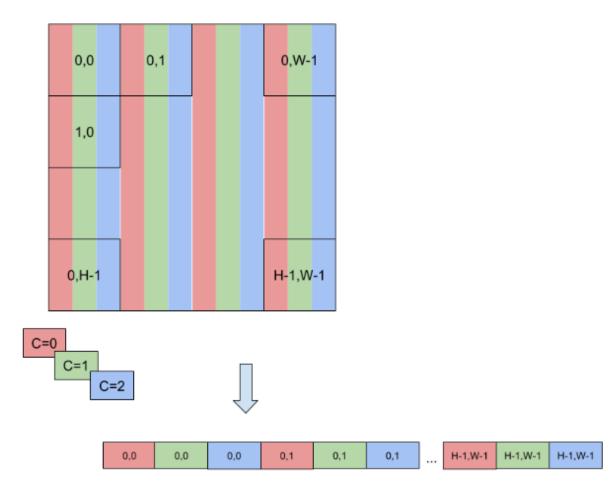

| Figure 23. | Layout format for HWC                                                         | 162 |

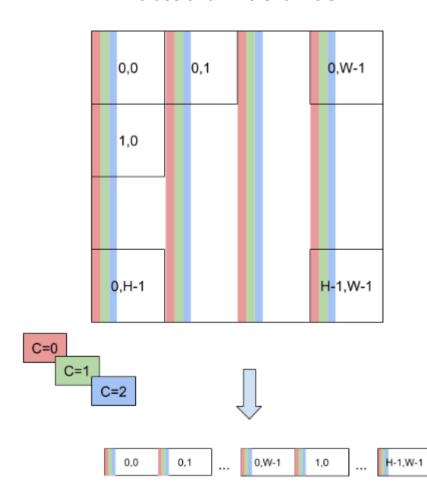

| •          | Values of #C/2# HxW Matrices are Pairs of Values of Two Consecutive           | 163 |

| _          | In NHWC8 Format, the Entries of an HxW Matrix Include the Values of all nnels | 164 |

| Figure 26. | Performance Metrics in a Normal trtexec Run under Nsight Systems              | 166 |

# List of Tables

| Table 1. | Supported I/O Formats                                          | 37  |

|----------|----------------------------------------------------------------|-----|

| Table 2. | Implicit Vs Explicit Quantization                              | 45  |

| Table 3. | Base Classes, Ordered from Least Expressive to Most Expressive | 76  |

| Table 4. | Differences Between Three Performance Approaches               | 139 |

| Table 5. | Types of Tensor Cores                                          | 142 |

# Chapter 1. Introduction

NVIDIA® TensorRT™ is an SDK that facilitates high-performance machine learning inference. It is designed to work in a complementary fashion with training frameworks such as TensorFlow, PyTorch, and MXNet. It focuses specifically on running an alreadytrained network quickly and efficiently on NVIDIA hardware.

### Structure of This Guide

Chapter 1 provides information about how TensorRT is packaged and supported, and how it fits into the developer ecosystem.

Chapter 2 provides a broad overview of TensorRT capabilities.

Chapters three and four contain introductions to the C++ and Python APIs respectively.

Subsequent chapters provide more detail about advanced features.

The appendix contains a layer reference and answers to FAQs.

# 1.2. Samples

You can find the safety samples in the /usr/src/tensorrt/samples package directory. For more information, refer to the NVIDIA TensorRT 8.6.10 Safety Developer Guide Supplement for DRIVE OS.

# Complementary GPU Features

Multi-Instance GPU, or MIG, is a feature of NVIDIA GPUs with NVIDIA Ampere Architecture or later architectures that enable user-directed partitioning of a single GPU into multiple smaller GPUs. The physical partitions provide dedicated compute and memory slices with QoS and independent execution of parallel workloads on fractions of the GPU. For TensorRT applications with low GPU utilization, MIG can produce higher throughput at small or no impact on latency. The optimal partitioning scheme is application-specific.

#### 1.4. Complementary Software

The NVIDIA Triton<sup>™</sup> Inference Server is a higher-level library providing optimized inference across CPUs and GPUs. It provides capabilities for starting and managing multiple models, and REST and gRPC endpoints for serving inference.

NVIDIA DALI<sup>e</sup> provides high-performance primitives for preprocessing image, audio, and video data. TensorRT inference can be integrated as a custom operator in a DALI pipeline. A working example of TensorRT inference integrated as a part of DALI can be found here.

TensorFlow-TensorRT (TF-TRT) is an integration of TensorRT directly into TensorFlow. It selects subgraphs of TensorFlow graphs to be accelerated by TensorRT, while leaving the rest of the graph to be executed natively by TensorFlow. The result is still a TensorFlow graph that you can execute as usual. For TF-TRT examples, refer to Examples for TensorRT in TensorFlow.

<u>Torch-TensorRT</u> (<u>Torch-TRT</u>) is a PyTorch-TensorRT compiler that converts PyTorch modules into TensorRT engines. Internally, the PyTorch modules are first converted into TorchScript/FX modules based on the Intermediate Representation (IR) selected. The compiler selects subgraphs of the PyTorch graphs to be accelerated by TensorRT, while leaving the rest of the graph to be executed natively by Torch. The result is still a PyTorch module that you can execute as usual. For examples, refer to Examples for Torch-TRT.

The TensorFlow-Quantization Toolkit provides utilities for training and deploying Tensorflow 2-based Keras models at reduced precision. This toolkit is used to quantize different layers in the graph exclusively based on operator names, class, and pattern matching. The quantized graph can then be converted into ONNX and then into TensorRT engines. For examples, refer to the model zoo.

The PyTorch Quantization Toolkit provides facilities for training PyTorch models at reduced precision, which can then be exported for optimization in TensorRT.

In addition, the PyTorch Automatic SParsity (ASP) tool provides facilities for training models with structured sparsity, which can then be exported and allows TensorRT to use the faster sparse tactics on NVIDIA Ampere Architecture GPUs.

TensorRT is integrated with NVIDIA's profiling tools, NVIDIA Nsight<sup>™</sup> Systems and NVIDIA Deep Learning Profiler (DLProf).

A restricted subset of TensorRT is certified for use in NVIDIA DRIVE products. Some APIs are marked for use only in NVIDIA DRIVE and are not supported for general use.

### 1.5. ONNX

TensorRT's primary means of importing a trained model from a framework is through the **ONNX** interchange format. TensorRT ships with an ONNX parser library to assist in importing models. Where possible, the parser is backward compatible up to opset 7; the ONNX Model Opset Version Converter can assist in resolving incompatibilities.

The <u>GitHub version</u> may support later opsets than the version shipped with TensorRT refer to the ONNX-TensorRT operator support matrix for the latest information on the supported opset and operators.

The ONNX operator support list for TensorRT can be found here.

PyTorch natively supports ONNX export. For TensorFlow, the recommended method is tf2onnx.

A good first step after exporting a model to ONNX is to run constant folding using Polygraphy. This can often solve TensorRT conversion issues in the ONNX parser and generally simplify the workflow. For details, refer to this example. In some cases, it may be necessary to modify the ONNX model further, for example, to replace subgraphs with plugins or reimplement unsupported operations in terms of other operations. To make this process easier, you can use <u>ONNX-GraphSurgeon</u>.

#### 1.6. Code Analysis Tools

For quidance using the valgrind and clang sanitizer tools with TensorRT, refer to the Troubleshooting chapter.

# 1.7. API Versioning

TensorRT version number (MAJOR.MINOR.PATCH) follows Semantic Versioning 2.0.0 for its public APIs and library ABIs. Version numbers change as follows:

- 1. MAJOR version when making incompatible API or ABI changes

- 2. MINOR version when adding functionality in a backward compatible manner

- 3. PATCH version when making backward compatible bug fixes

Note that semantic versioning does not extend to serialized objects. To reuse plan files, and timing caches, version numbers must match across major, minor, patch, and build versions (with some exceptions for the safety runtime as detailed in the NVIDIA DRIVE OS 6.0 Developer Guide). Calibration caches can typically be reused within a major version but compatibility is not quaranteed.

#### **Deprecation Policy** 1.8.

Deprecation is used to inform developers that some APIs and tools are no longer recommended for use. Beginning with version 8.0, TensorRT has the following deprecation policy:

- Deprecation notices are communicated in the NVIDIA TensorRT 8.6.10 Release Notes for DRIVE OS.

- ▶ When using the C++ API:

- ▶ API functions are marked with the TRT DEPRECATED API macro.

- Enums are marked with the TRT DEPRECATED ENUM macro.

- All other locations are marked with the TRT DEPRECATED macro.

- Classes, functions, and objects will have a statement documenting when they were deprecated.

- When using the Python API, deprecated methods and classes will issue deprecation warnings at runtime, if they are used.

- TensorRT provides a 12-month migration period after the deprecation.

- APIs and tools continue to work during the migration period.

- After the migration period ends, APIs and tools are removed in a manner consistent with semantic versioning.

For any APIs and tools specifically deprecated in TensorRT 7.x, the 12-month migration period starts from the TensorRT 8.0 GA release date.

# Hardware Support Lifetime

TensorRT 8.5.3 was the last release supporting NVIDIA Kepler (SM 3.x) and NVIDIA Maxwell (SM 5.x) devices. These devices are no longer supported in TensorRT 8.6. NVIDIA Pascal (SM 6.x) devices are deprecated in TensorRT 8.6.

# 1.10. Support

Support, resources, and information about TensorRT can be found online at https:// <u>developer.nvidia.com/tensorrt</u>. This includes blogs, samples, and more.

In addition, you can access the NVIDIA DevTalk TensorRT forum at https:// devtalk.nvidia.com/default/board/304/tensorrt/ for all things related to TensorRT. This forum offers the possibility of finding answers, making connections, and getting involved in discussions with customers, developers, and TensorRT engineers.

# 1.11. Reporting Bugs

NVIDIA appreciates all types of feedback. If you encounter any problems, follow the instructions in the Reporting TensorRT Issues section to report the issues.

# Chapter 2. TensorRT's Capabilities

This chapter provides an overview of what you can do with TensorRT. It is intended to be useful to all TensorRT users.

# 2.1. C++ and Python APIs

TensorRT's API has language bindings for both C++ and Python, with nearly identical capabilities. The Python API facilitates interoperability with Python data processing toolkits and libraries like NumPy and SciPy. The C++ API can be more efficient, and may better meet some compliance requirements, for example in automotive applications.

Note: The Python API is not available for all platforms.

For more information, refer to the NVIDIA TensorRT 8.6.10 API Reference for DRIVE OS.

#### The Programming Model 2.2.

TensorRT operates in two phases. In the first phase, usually performed offline, you provide TensorRT with a model definition, and TensorRT optimizes it for a target GPU. In the second phase, you use the optimized model to run inference.

#### The Build Phase 221

The highest-level interface for the build phase of TensorRT is the Builder. The builder is responsible for optimizing a model, and producing an *Engine*.

In order to build an engine, you must:

- Create a network definition.

- Specify a configuration for the builder.

- Call the builder to create the engine.

The NetworkDefinition interface is used to define the model. The most common path to transfer a model to TensorRT is to export it from a framework in ONNX format, and use TensorRT's ONNX parser to populate the network definition. However, you can also construct the definition step by step using TensorRT's Layer and Tensor interfaces.

Whichever way you choose, you must also define which tensors are the inputs and outputs of the network. Tensors that are not marked as outputs are considered to be transient values that can be optimized away by the builder. Input and output tensors must be named, so that at runtime, TensorRT knows how to bind the input and output buffers to the model.

The BuilderConfig interface is used to specify how TensorRT should optimize the model. Among the configuration options available, you can control TensorRT's ability to reduce the precision of calculations, control the tradeoff between memory and runtime execution speed, and constrain the choice of CUDA® kernels. Since the builder can take minutes or more to run, you can also control how the builder searches for kernels, and cached search results for use in subsequent runs.

After you have a network definition and a builder configuration, you can call the builder to create the engine. The builder eliminates dead computations, folds constants, and reorders and combines operations to run more efficiently on the GPU. It can optionally reduce the precision of floating-point computations, either by simply running them in 16-bit floating point, or by quantizing floating point values so that calculations can be performed using 8-bit integers. It also times multiple implementations of each layer with varying data formats, then computes an optimal schedule to execute the model, minimizing the combined cost of kernel executions and format transforms.

The builder creates the engine in a serialized form called a *plan*, which can be deserialized immediately, or saved to disk for later use.

#### Note:

- By default, engines created by TensorRT are specific to both the TensorRT version with which they were created and the GPU on which they were created. Refer to the Version Compatibility and Hardware Compatibility sections for how to configure an engine for forward compatibility.

- TensorRT's network definition does not deep-copy parameter arrays (such as the weights for a convolution). Therefore, you must not release the memory for those arrays until the build phase is complete. When importing a network using the ONNX parser, the parser owns the weights, so it must not be destroyed until the build phase is complete.

- The builder times algorithms to determine the fastest. Running the builder in parallel with other GPU work may perturb the timings, resulting in poor optimization.

#### 2.2.2. The Runtime Phase

The highest-level interface for the execution phase of TensorRT is the Runtime.

When using the runtime, you will typically carry out the following steps:

- Deserialize a plan to create an engine.

- Create an execution context from the engine.

Then, repeatedly:

Populate input buffers for inference.

▶ Call engueue V3 () on the execution context to run inference.

The Engine interface represents an optimized model. You can guery an engine for information about the input and output tensors of the network - the expected dimensions, data type, data format, and so on.

The ExecutionContext interface, created from the engine is the main interface for invoking inference. The execution context contains all of the state associated with a particular invocation - thus you can have multiple contexts associated with a single engine, and run them in parallel.

When invoking inference, you must set up the input and output buffers in the appropriate locations. Depending on the nature of the data, this may be in either CPU or GPU memory. If not obvious based on your model, you can guery the engine to determine in which memory space to provide the buffer.

After the buffers are set up, inference can be enqueued (enqueueV3). The required kernels are engueued on a CUDA stream, and control is returned to the application as soon as possible. Some networks require multiple control transfers between CPU and GPU, so control may not return immediately. To wait for completion of asynchronous execution. synchronize on the stream using cudaStreamSynchronize.

# 2.3. Plugins

TensorRT has a Plugin interface to allow applications to provide implementations of operations that TensorRT does not support natively. Plugins that are created and registered with TensorRT's PluginRegistry can be found by the ONNX parser while translating the network.

TensorRT ships with a library of plugins, and source for many of these and some additional plugins can be found here.

You can also write your own plugin library and serialize it with the engine.

Refer to the Extending TensorRT with Custom Layers chapter for more details.

# Types and Precision

TensorRT supports computations using FP32, FP16, INT8, Bool, and INT32 data types. 1

When TensorRT chooses CUDA kernels to implement floating point operations in the network, it defaults to FP32 implementations. There are two ways to configure different levels of precision:

To control precision at the model level, BuilderFlag options can indicate to TensorRT that it may select lower-precision implementations when searching for the fastest (and because lower precision is generally faster, if allowed to, it typically will).

TensorRT 8.6 adds nvinfer1::DataType::kFP8 to the public API in preparation for the introduction of FP8 support in future TensorRT releases. However, FP8 (8-bit floating point) is not supported by TensorRT currently and attempting to use FP8 will result in an error or undefined behavior.

- Therefore, you can easily instruct TensorRT to use FP16 calculations for your entire model. For regularized models whose input dynamic range is approximately one, this typically produces significant speedups with negligible change in accuracy.

- For finer-grained control, where a layer must run at higher precision because part of the network is numerically sensitive or requires high dynamic range, arithmetic precision can be specified for that layer.

Refer to the Reduced Precision section for more details.

### 2.5. Quantization

TensorRT supports quantized floating point, where floating-point values are linearly compressed and rounded to 8-bit integers. This significantly increases arithmetic throughput while reducing storage requirements and memory bandwidth. When quantizing a floating-point tensor, TensorRT must know its dynamic range - that is, what range of values is important to represent - values outside this range are clamped when quantizing.

Dynamic range information can be calculated by the builder (this is called *calibration*) based on representative input data. Or you can perform quantization-aware training in a framework and import the model to TensorRT with the necessary dynamic range information.

Refer to the Working with INT8 chapter for more details.

#### Tensors and Data Formats 2.6.

When defining a network, TensorRT assumes that tensors are represented by multidimensional C-style arrays. Each layer has a specific interpretation of its inputs: for example, a 2D convolution will assume that the last three dimensions of its input are in CHW format - there is no option to use, for example a WHC format. Refer to NVIDIA TensorRT Operator's Reference for how each layer interprets its inputs.

Note that tensors are limited to at most 2^31-1 elements.

While optimizing the network, TensorRT performs transformations internally (including to HWC, but also more complex formats) to use the fastest possible CUDA kernels. In general, formats are chosen to optimize performance, and applications have no control over the choices. However, the underlying data formats are exposed at I/O boundaries (network input and output, and passing data to and from plugins) to allow applications to minimize unnecessary format transformations.

Refer to the I/O Formats section for more details.

# **Dynamic Shapes**

By default, TensorRT optimizes the model based on the input shapes (batch size, image size, and so on) at which it was defined. However, the builder can be configured to allow the input dimensions to be adjusted at runtime. In order to enable this, you specify one or more instances of OptimizationProfile in the builder configuration, containing for each input a minimum and maximum shape, along with an optimization point within that range.

TensorRT creates an optimized engine for each profile, choosing CUDA kernels that work for all shapes within the [minimum, maximum] range and are fastest for the optimization point - typically different kernels for each profile. You can then select among profiles at runtime.

Refer to the Working with Dynamic Shapes chapter for more details.

#### 2.8. DLA

TensorRT supports NVIDIA's Deep Learning Accelerator (DLA), a dedicated inference processor present on many NVIDIA SoCs that supports a subset of TensorRT's layers. TensorRT allows you to execute part of the network on the DLA and the rest on GPU; for layers that can be executed on either device, you can select the target device in the builder configuration on a per-layer basis.

Refer to the Working with DLA chapter for more details.

# 2.9. Updating Weights

When building an engine, you can specify that it may later have its weights updated. This can be useful if you are frequently updating the weights of the model without changing the structure, such as in reinforcement learning or when retraining a model while retaining the same structure. Weight updates are performed using the Refitter interface.

Refer to the Refitting an Engine section for more details.

### 2.10. trtexec Tool

Included in the samples directory is a command-line wrapper tool called trtexec. trtexec is a tool to use TensorRT without having to develop your own application. The trtexec tool has three main purposes:

- benchmarking networks on random or user-provided input data.

- generating serialized engines from models.

- generating a serialized timing cache from the builder.

Refer to the trtexec section for more details.

# 2.11. Polygraphy

Polygraphy is a toolkit designed to assist in running and debugging deep learning models in TensorRT and other frameworks. It includes a Python API and a command-line interface (CLI) built using this API.

Among other things, with Polygraphy you can:

- ▶ Run inference among multiple backends, like TensorRT and ONNX-Runtime, and compare results (for example API,CLI).

- ► Convert models to various formats, for example, TensorRT engines with post-training quantization (for example API,CLI).

- View information about various types of models (for example <u>CLI</u>)

- Modify ONNX models on the command line:

- Extract subgraphs (for example <u>CLI</u>).

- Simplify and sanitize (for example CLI).

- ▶ Isolate faulty tactics in TensorRT (for example <u>CLI</u>).

For more details, refer to the Polygraphy repository.

# Chapter 3. The C++ API

This chapter illustrates basic usage of the C++ API, assuming you are starting with an ONNX model. sampleOnnxMNIST illustrates this use case in more detail.

The C++ API can be accessed through the header NvInfer.h, and is in the nvinfer1 namespace. For example, a simple application might begin with:

```

#include "NvInfer.h"

using namespace nvinfer1;

```

Interface classes in the TensorRT C++ API begin with the prefix I, for example ILogger,

A CUDA context is automatically created the first time TensorRT makes a call to CUDA, if none exists before that point. It is generally preferable to create and configure the CUDA context yourself before the first call to TensorRT.

In order to illustrate object lifetimes, code in this chapter does not use smart pointers; however, their use is recommended with TensorRT interfaces.

### 3.1. The Build Phase

To create a builder, you first must instantiate the ILogger interface. This example captures all warning messages but ignores informational messages:

```

class Logger : public ILogger

void log(Severity severity, const char* msg) noexcept override

// suppress info-level messages

if (severity <= Severity::kWARNING)</pre>

std::cout << msg << std::endl;</pre>

}

```

You can then create an instance of the builder:

IBuilder\* builder = createInferBuilder(logger);

### Creating a Network Definition

After the builder has been created, the first step in optimizing a model is to create a network definition:

```

uint32 t flag = 1U << static cast<uint32 t>

(NetworkDefinitionCreationFlag::kEXPLICIT BATCH);

```

#### INetworkDefinition\* network = builder->createNetworkV2(flag)

The REXPLICIT BATCH flag is required in order to import models using the ONNX parser. Refer to the Explicit Versus Implicit Batch section for more information.

#### Importing a Model Using the ONNX Parser 3.1.2.

Now, the network definition must be populated from the ONNX representation. The ONNX parser API is in the file NyonnxParser.h, and the parser is in the nyonnxparser C++ namespace.

```

#include "NvOnnxParser.h"

using namespace nvonnxparser;

```

You can create an ONNX parser to populate the network as follows:

```

IParser* parser = createParser(*network, logger);

```

Then, read the model file and process any errors.

```

parser->parseFromFile(modelFile,

static_cast<int32_t>(ILogger::Severity::kWARNING));

for (int32 t i = 0; i < parser.getNbErrors(); ++i)</pre>

std::cout << parser->getError(i)->desc() << std::endl;</pre>

```

An important aspect of a TensorRT network definition is that it contains pointers to model weights, which are copied into the optimized engine by the builder. Since the network was created using the parser, the parser owns the memory occupied by the weights, and so the parser object should not be deleted until after the builder has run.

#### **Building an Engine** 3.1.3.

The next step is to create a build configuration specifying how TensorRT should optimize the model.

```

IBuilderConfig* config = builder->createBuilderConfig();

```

This interface has many properties that you can set in order to control how TensorRT optimizes the network. One important property is the maximum workspace size. Layer implementations often require a temporary workspace, and this parameter limits the maximum size that any layer in the network can use. If insufficient workspace is provided, it is possible that TensorRT will not be able to find an implementation for a layer. By default the workspace is set to the total global memory size of the given device; restrict it when necessary, for example, when multiple engines are to be built on a single device.

```

config->setMemoryPoolLimit(MemoryPoolType::kWORKSPACE, 1U << 20);</pre>

```

Once the configuration has been specified, the engine can be built.

```

IHostMemory* serializedModel = builder->buildSerializedNetwork(*network, *config);

```

Since the serialized engine contains the necessary copies of the weights, the parser, network definition, builder configuration and builder are no longer necessary and may be safely deleted:

```

delete parser;

delete network;

delete config:

```

#### delete builder;

The engine can then be saved to disk, and the buffer into which it was serialized can be deleted.

delete serializedModel

Note: Serialized engines are not portable across platforms or TensorRT versions. Engines are specific to the exact GPU model that they were built on (in addition to the platform and the TensorRT version).

Since building engines is intended as an offline process, it can take significant time. Refer to the Optimizing Builder Performance section for how to make the builder run faster.

#### Deserializing a Plan 3.2.

Assuming you have previously serialized an optimized model and want to perform inference, you must create an instance of the Runtime interface. Like the builder, the runtime requires an instance of the logger:

IRuntime\* runtime = createInferRuntime(logger);

After you have read the model into a buffer, you can deserialize it to obtain an engine:

ICudaEngine\* engine =

runtime->deserializeCudaEngine(modelData, modelSize);

# **Performing Inference**

The engine holds the optimized model, but to perform inference we must manage additional state for intermediate activations. This is done using the ExecutionContext interface:

IExecutionContext \*context = engine->createExecutionContext();

An engine can have multiple execution contexts, allowing one set of weights to be used for multiple overlapping inference tasks. (A current exception to this is when using dynamic shapes, when each optimization profile can only have one execution context, unless the preview feature, kprofile sharing 0806, is specified.)

To perform inference, you must pass TensorRT buffers for input and output, which TensorRT requires you to specify with calls to setTensorAddress, which takes the name of the tensor and the address of the buffer. You can query the engine using the names you provided for input and output tensors to find the right positions in the array:

context->setTensorAddress(INPUT NAME, inputBuffer); context->setTensorAddress(OUTPUT\_NAME, outputBuffer);

You can then call TensorRT's method enqueuev3 to start inference using a CUDA stream: context->enqueueV3(stream);

A network will be executed asynchronously or not depending on the structure and features of the network. A non-exhaustive list of features that can cause synchronous behavior are data dependent shapes, DLA usage, loops, and plugins that are synchronous, for example. It is common to enqueue data transfers with  ${\tt cudaMemcpyAsync}$  () before and after the kernels to move data from the GPU if it is not already there.

To determine when the kernels (and possibly cudaMemcpyAsync()) are complete, use standard CUDA synchronization mechanisms such as events or waiting on the stream.

# Chapter 4. The Python API

This chapter illustrates basic usage of the Python API, assuming you are starting with an ONNX model. The onnx resnet50.py sample illustrates this use case in more detail.

The Python API can be accessed through the tensorrt module:

import tensorrt as trt

### 4.1. The Build Phase

To create a builder, you must first create a logger. The Python bindings include a simple logger implementation that logs all messages preceding a certain severity to stdout.

```

logger = trt.Logger(trt.Logger.WARNING)

```

Alternatively, it is possible to define your own implementation of the logger by deriving from the ILogger class:

```

class MyLogger(trt.ILogger):

def __init__(self):

trt.ILogger. init (self)

def log(self, severity, msg):

pass # Your custom logging implementation here

logger = MyLogger()

```

You can then create a builder:

```

builder = trt.Builder(logger)

```

Since building engines is intended as an offline process, it can take significant time. Refer to the Optimizing Builder Performance section for how to make the builder run faster.

#### Creating a Network Definition in Python 4.1.1.

After the builder has been created, the first step in optimizing a model is to create a network definition:

```

network = builder.create network(1 << int(trt.NetworkDefinitionCreationFlag.EXPLICIT BATCH))</pre>

```

The EXPLICIT BATCH flag is required in order to import models using the ONNX parser. Refer to the Explicit Versus Implicit Batch section for more information.

### 4.1.2. Importing a Model Using the ONNX Parser

Now, the network definition must be populated from the ONNX representation. You can create an ONNX parser to populate the network as follows:

```

parser = trt.OnnxParser(network, logger)

```

Then, read the model file and process any errors:

```

success = parser.parse_from_file(model_path)

for idx in range(parser.num_errors):

print(parser.get error(idx))

if not success:

pass # Error handling code here

```

### **Building an Engine**

The next step is to create a build configuration specifying how TensorRT should optimize the model:

```

config = builder.create_builder_config()

```

This interface has many properties that you can set in order to control how TensorRT optimizes the network. One important property is the maximum workspace size. Layer implementations often require a temporary workspace, and this parameter limits the maximum size that any layer in the network can use. If insufficient workspace is provided, it is possible that TensorRT will not be able to find an implementation for a layer. By default, the workspace is set to the total global memory size of the given device; restrict it when necessary, for example, when multiple engines are to be built on a single device.

```

config.set_memory_pool_limit(trt.MemoryPoolType.WORKSPACE, 1 << 20) # 1 MiB</pre>

```

After the configuration has been specified, the engine can be built and serialized with: serialized\_engine = builder.build\_serialized\_network(network, config)

It may be useful to save the engine to a file for future use. You can do that like so:

```

with open("sample.engine", "wb") as f:

f.write(serialized_engine)

```

Note: Serialized engines are not portable across platforms or TensorRT versions. Engines are specific to the exact GPU model that they were built on (in addition to the platform and the TensorRT version).

# Deserializing a Plan

To perform inference, deserialize the engine using the Runtime interface. Like the builder, the runtime requires an instance of the logger.

```

runtime = trt.Runtime(logger)

```

You can then deserialize the engine from a memory buffer:

```

engine = runtime.deserialize_cuda_engine(serialized_engine)

```

If you want, first load the engine from a file:

with open("sample.engine", "rb") as f: serialized engine = f.read()

# **Performing Inference**

The engine holds the optimized model, but to perform inference requires additional state for intermediate activations. This is done using the <code>IExecutionContext</code> interface:

#### context = engine.create execution context()

An engine can have multiple execution contexts, allowing one set of weights to be used for multiple overlapping inference tasks. (A current exception to this is when using dynamic shapes, when each optimization profile can only have one execution context, unless the preview feature, PROFILE SHARING 0806, is specified.)

To perform inference, you must specify buffers for inputs and outputs:

#### context.set\_tensor\_address(name, ptr)

Several Python packages allow you to allocate memory on the GPU, including, but not limited to, the official CUDA Python bindings, PyTorch, cuPy, and Numba.

After populating the input buffer, you can call TensorRT's execute async v3 method to start inference using a CUDA stream. A network will be executed asynchronously or not depending on the structure and features of the network. A non-exhaustive list of features that can cause synchronous behavior are data dependent shapes, DLA usage, loops, and plugins that are synchronous, for example.

First, create the CUDA stream. If you already have a CUDA stream, you can use a pointer to the existing stream. For example, for PyTorch CUDA streams, that is, torch.cuda.Stream(), you can access the pointer using the cuda stream property; for Polygraphy CUDA streams, use the ptr attribute; or you can create a stream using CUDA Python binding directly by calling <a href="mailto:cudaStreamCreate()">cudaStreamCreate()</a>.

Next, start inference:

#### context.execute async v3(buffers, stream ptr)

It is common to enqueue asynchronous transfers (cudaMemcpyAsync()) before and after the kernels to move data from the GPU if it is not already there.

To determine when inference (and asynchronous transfers) are complete, use the standard CUDA synchronization mechanisms such as events or waiting on the stream. For example, with PyTorch CUDA streams or Polygraphy CUDA streams, issue stream.synchronize(). With streams created with CUDA Python binding, issue cudaStreamSynchronize(stream).

# Chapter 5. How TensorRT Works

This chapter provides more detail on how TensorRT works.

# 5.1. Object Lifetimes

TensorRT's API is class-based, with some classes acting as factories for other classes. For objects owned by the user, the lifetime of a factory object must span the lifetime of objects it creates. For example, the NetworkDefinition and BuilderConfig classes are created from the Builder class, and objects of those classes should be destroyed before the builder factory object.

An important exception to this rule is creating an engine from a builder. After you have created an engine, you may destroy the builder, network, parser, and build config and continue using the engine.

# **Error Handling and Logging**

When creating TensorRT top-level interfaces (builder, runtime or refitter), you must provide an implementation of the Logger interface. The logger is used for diagnostics and informational messages; its verbosity level is configurable. Since the logger may be used to pass back information at any point in the lifetime of TensorRT, its lifetime must span any use of that interface in your application. The implementation must also be threadsafe, since TensorRT may use worker threads internally.

An API call to an object will use the logger associated with the corresponding top-level interface. For example, in a call to ExecutionContext::enqueueV3(), the execution context was created from an engine, which was created from a runtime, so TensorRT will use the logger associated with that runtime.

The primary method of error handling is the ErrorRecorder interface. You can implement this interface, and attach it to an API object to receive errors associated with that object. The recorder for an object will also be passed to any others it creates - for example, if you attach an error recorder to an engine, and create an execution context from that engine, it will use the same recorder. If you then attach a new error recorder to the execution context, it will receive only errors coming from that context. If an error is generated but no error recorder is found, it will be emitted through the associated logger.

Note that CUDA errors are generally asynchronous - so when performing multiple inferences or other streams of CUDA work asynchronously in a single CUDA context, an asynchronous GPU error may be observed in a different execution context than the one that generated it.

# 5.3. Memory

TensorRT uses considerable amounts of device memory, (that is, memory directly accessible by the GPU, as opposed to the host memory attached to the CPU). Since device memory is often a constrained resource, it is important to understand how TensorRT uses it.

#### 5.3.1. The Build Phase

During build, TensorRT allocates device memory for timing layer implementations. Some implementations can consume a large amount of temporary memory, especially with large tensors. You can control the maximum amount of temporary memory through the memory pool limits of the builder config. The workspace size defaults to the full size of device global memory but can be restricted when necessary. If the builder finds applicable kernels that could not be run because of insufficient workspace, it will emit a logging message indicating this.

Even with relatively little workspace however, timing requires creating buffers for input, output, and weights. TensorRT is robust against the operating system (OS) returning outof-memory for such allocations. On some platforms the OS may successfully provide memory, which then the out-of-memory killer process observes that the system is low on memory, and kills TensorRT. If this happens free up as much system memory as possible before retrying.

During the build phase, there will typically be at least two copies of the weights in host memory: those from the original network, and those included as part of the engine as it is built. In addition, when TensorRT combines weights (for example convolution with batch normalization) additional temporary weight tensors will be created.

#### 5.3.2. The Runtime Phase

At runtime, TensorRT uses relatively little host memory, but can use considerable amounts of device memory.

An engine, on deserialization, allocates device memory to store the model weights. Since the serialized engine is almost all weights, its size is a good approximation to the amount of device memory the weights require.

An ExecutionContext uses two kinds of device memory:

Persistent memory required by some layer implementations - for example, some convolution implementations use edge masks, and this state cannot be shared between contexts as weights are, because its size depends on the layer input shape, which may vary across contexts. This memory is allocated on creation of the execution context, and lasts for its lifetime.

Scratch memory, used to hold intermediate results while processing the network. This memory is used for intermediate activation tensors. It is also used for temporary storage required by layer implementations, the bound for which is controlled by IBuilderConfig::setMemoryPoolLimit().

You may optionally create an execution context without scratch memory using ICudaEngine::createExecutionContextWithoutDeviceMemory() and provide that memory yourself for the duration of network execution. This allows you to share it between multiple contexts that are not running concurrently, or for other uses while inference is not running. The amount of scratch memory required is returned by ICudaEngine::getDeviceMemorySize().

Information about the amount of persistent memory and scratch memory used by the execution context is emitted by the builder when building the network, at severity kINFO. Examining the log, the messages look similar to the following:

```

[08/12/2021-17:39:11] [I] [TRT] Total Host Persistent Memory: 106528

[08/12/2021-17:39:11] [I] [TRT] Total Device Persistent Memory: 29785600

[08/12/2021-17:39:11] [I] [TRT] Total Scratch Memory: 9970688

```

By default, TensorRT allocates device memory directly from CUDA. However, you can attach an implementation of TensorRT's IGpuAllocator interface to the builder or runtime and manage device memory yourself. This is useful if your application wants to control all GPU memory and suballocate to TensorRT instead of having TensorRT allocate directly from CUDA.

TensorRT's dependencies (NVIDIA cuDNN and NVIDIA cuBLAS) can occupy large amounts of device memory. TensorRT allows you to control whether these libraries are used for inference by using the TacticSources attribute in the builder configuration. Note that some plugin implementations require these libraries, so that when they are excluded, the network may not be compiled successfully.

In addition, PreviewFeature::kDISABLE EXTERNAL TACTIC SOURCES FOR CORE 0805 is used to control the usage of cuDNN, cuBLAS, and cuBLASLt in the TensorRT core library. When this flag is set, the TensorRT core library will not use these tactics even if they are specified by IBuilderConfig::setTacticSources(). This flag will not affect the cudnnContext and cublasContext handles passed to the plugins using IPluginV2Ext::attachToContext() if the appropriate tactic sources are set. This flag is set by default.

The CUDA infrastructure and TensorRT's device code also consume device memory. The amount of memory varies by platform, device, and TensorRT version. You can use cudaGetMemInfo to determine the total amount of device memory in use.

TensorRT measures the amount of memory in use before and after critical operations in builder and runtime. These memory usage statistics are printed to TensorRT's information logger. For example:

```

[MemUsageChange] Init CUDA: CPU +535, GPU +0, now: CPU 547, GPU 1293 (MiB)

```

It indicates the memory use change by CUDA initialization. CPU +535, GPU +0 is the increased amount of memory after running CUDA initialization. The content after now: is the CPU/GPU memory usage snapshot after CUDA initialization.

Note: In a multi-tenant situation, the reported memory use by cudaGetMemInfo and TensorRT is prone to race conditions where a new allocation/free done by a different process or a different thread. Since CUDA is not in control of memory on unified-memory devices, the results returned by <code>cudaGetMemInfo</code> may not be accurate on these platforms.

### 5.3.3. CUDA Lazy Loading

CUDA lazy loading is a CUDA feature that can significantly reduce the peak GPU and host memory usage of TensorRT and speed up TensorRT initialization with negligible (< 1%) performance impact. The saving of memory usage and initialization time depends on the model, software stack, GPU platform, etc. It is enabled by setting the environment variable CUDA MODULE LOADING=LAZY. Refer to the NVIDIA CUDA documentation for more information.

### 5.3.4. L2 Persistent Cache Management

NVIDIA Ampere and later architectures support L2 cache persistence, a feature which allows prioritization of L2 cache lines for retention when a line is chosen for eviction. TensorRT can use this to retain activations in cache, reducing DRAM traffic, and power consumption.

Cache allocation is per-execution context, enabled using the context's setPersistentCacheLimit method. The total persistent cache among all contexts (and other components using this feature) should not exceed cudaDeviceProp::persistingL2CacheMaxSize. Refer to the NVIDIA CUDA Best Practices Guide for more information.

# 5.4. Threading

In general, TensorRT objects are not thread safe; accesses to an object from different threads must be serialized by the client.

The expected runtime concurrency model is that different threads will operate on different execution contexts. The context contains the state of the network (activation values, and so on) during execution, so using a context concurrently in different threads results in undefined behavior.

To support this model, the following operations are thread safe:

- Nonmodifying operations on a runtime or engine.

- Deserializing an engine from a TensorRT runtime.

- Creating an execution context from an engine.

- Registering and deregistering plugins.

There are no thread-safety issues with using multiple builders in different threads; however, the builder uses timing to determine the fastest kernel for the parameters provided, and using multiple builders with the same GPU will perturb the timing and TensorRT's ability to construct optimal engines. There are no such issues using multiple threads to build with different GPUs.

### 5.5. Determinism

The TensorRT builder uses timing to find the fastest kernel to implement a given operator. Timing kernels is subject to noise - other work running on the GPU, fluctuations in GPU clock speed, and so on. Timing noise means that on successive runs of the builder, the same implementation may not be selected.

In general, different implementations will use a different order of floating point operations, resulting in small differences in the output. The impact of these differences on the final result is usually very small. However, when TensorRT is configured to optimize by tuning over multiple precisions, the difference between an FP16 and an FP32 kernel can be more significant, particularly if the network has not been well regularized or is otherwise sensitive to numerical drift.

Other configuration options that can result in a different kernel selection are different input sizes (for example, batch size) or a different optimization point for an input profile (refer to the Working with Dynamic Shapes section).

The AlgorithmSelector interface allows you to force the builder to pick a particular implementation for a given layer. You can use this to ensure that the same kernels are picked by the builder from run to run. For more information, refer to the Algorithm Selection and Reproducible Builds section.

After an engine has been built, except for IFillLayer, it is deterministic: providing the same input in the same runtime environment will produce the same output.

### 5.5.1. IFillLayer Determinism

When IFillLayer is added to a network using either the RANDOM UNIFORM Or RANDOM NORMAL operations, the determinism guarantee above is no longer valid. On each invocation, these operations generate tensors based on the RNG state, and then update the RNG state. This state is stored on a per-execution context basis.

#### 5.6. **Runtime Options**

TensorRT provides multiple runtime libraries to meet a variety of use cases. C++ applications that run TensorRT engines should link against one of the following:

- ▶ The default runtime is the main library (libnvinfer.so/.dll).

- The lean runtime library (library lean.so/.dll) is much smaller than the default library, and contains only the code necessary to run a version-compatible engine. It has some restrictions; primarily, it cannot refit or serialize engines.

The dispatch runtime (libnvinfer dispatch.so/.dll) is a small shim library that can load a lean runtime, and redirect calls to it. The dispatch runtime is capable of loading older versions of the lean runtime, and together with appropriate configuration of the builder, can be used to provide compatibility between a newer version of TensorRT and an older plan file. Using the dispatch runtime is almost the same as manually loading the lean runtime, but it checks that APIs are implemented by the lean runtime loaded, and performs some parameter mapping to support API changes where possible.

The lean runtime contains fewer operator implementations than the default runtime. Since TensorRT chooses operator implementations at build time, you need to specify that the engine should be built for the lean runtime by enabling version compatibility. It may be slightly slower than an engine built for the default runtime.

The lean runtime contains all the functionality of the dispatch runtime, and the default runtime contains all the functionality of the lean runtime.